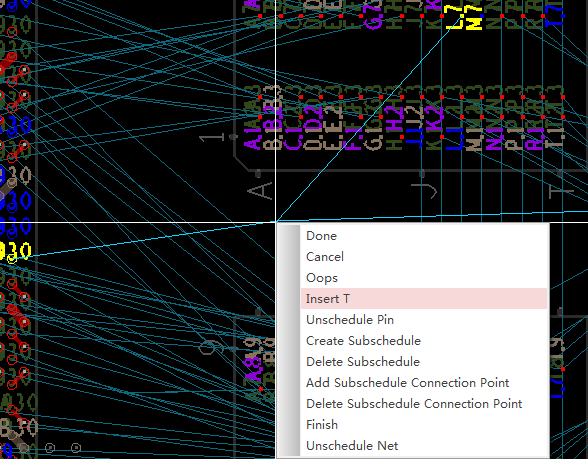

执行菜单命令“Logic”→“Net Schedule”,点击CPU端任意一个地址线网络,然后在中间某个位置右键,选择右键菜单中的Insert T,然后在需要添加T点的位置单击鼠标左键,如图所示。

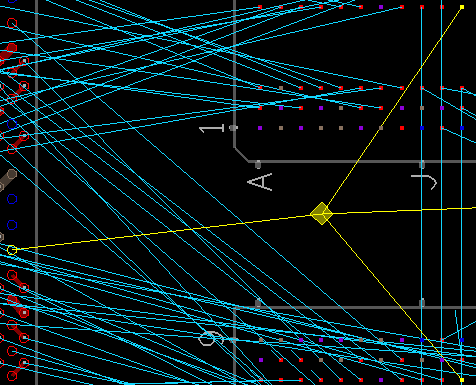

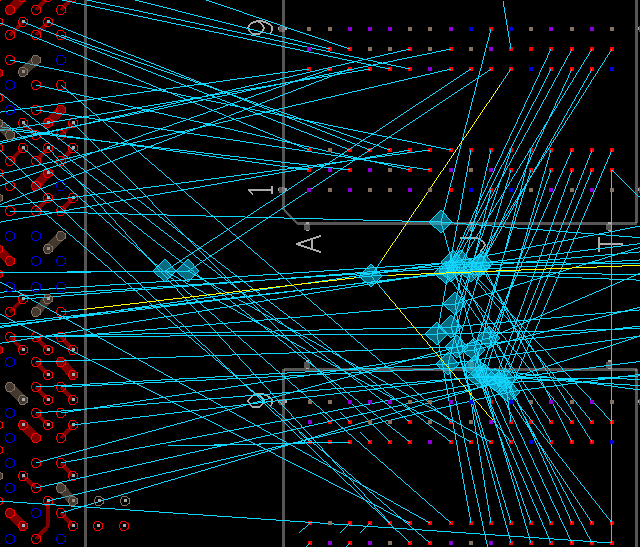

然后点击第二个pin,再回到T点,再点击第三个pin,右键Done,创建后的T点如图所示。

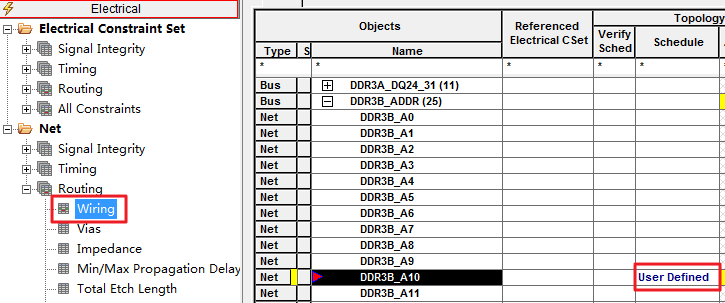

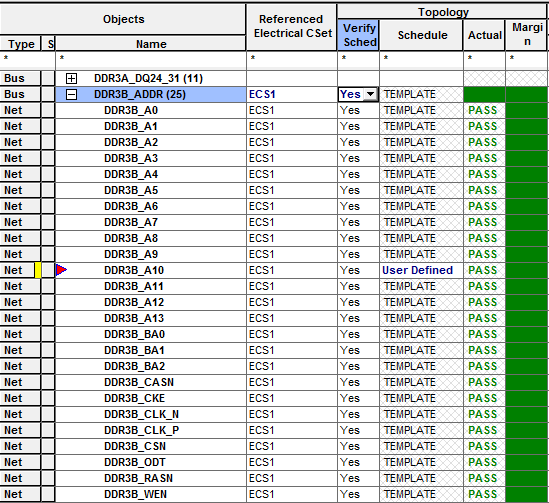

这只是创建一个地址线的T型连接点,如果需要整组地址线都创建,可进入CM管理器中,在Net-Routing-Wiring下面,刚才设置的网络拓扑变会显示成UserDefined,如图所示。

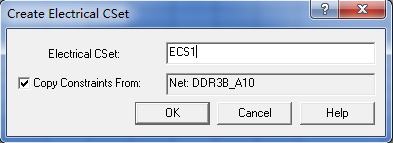

选中上图的DDR3B_A10网络,右键选择Create--Electrical CSet,将该网络创建好的T型连接点作为一个可供参考的电气规则。如图所示。

然后为整个地址线BUS选择步骤(4)中创建的ECSet作为参考,Verify Schedule选择yes即打开验证该BUS的地址线是否符合T型拓扑的结构特征,ok的会显示为pass,如图所示。

这时所有地址线都创建了T点,如图所示。

(2)T型等长规则的设置

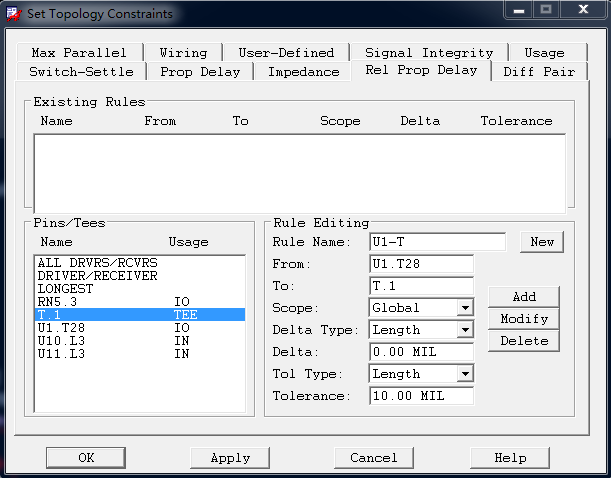

在CM管理器中选中地址选BUS,右键SigXplore。

进入拓扑结构的编辑界面,执行菜单命令“Set”→“Constraints”,选择Rel Prop Delay窗口,即可设置相应的等长规则。如图所示 。

(3)T型节点的删除

执行菜单命令“Logic”→“Net Schedule”,选择需要删除T点的网络,右键,选择Unschedule Net即可删除T点。