1 基于Check List的检查

出光绘文件之前一般要经过严格的检查流程,每个公司都有自己的Check List。包括原理图、元件封装、结构、布局、布线、生产工艺.....都要一一检查到位。任何一个环节出问题,都有可能导致最后的产品研发失败。

2 Dispaly Statues的检查

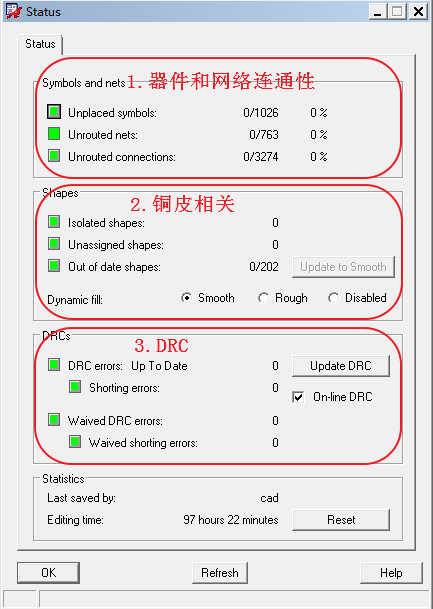

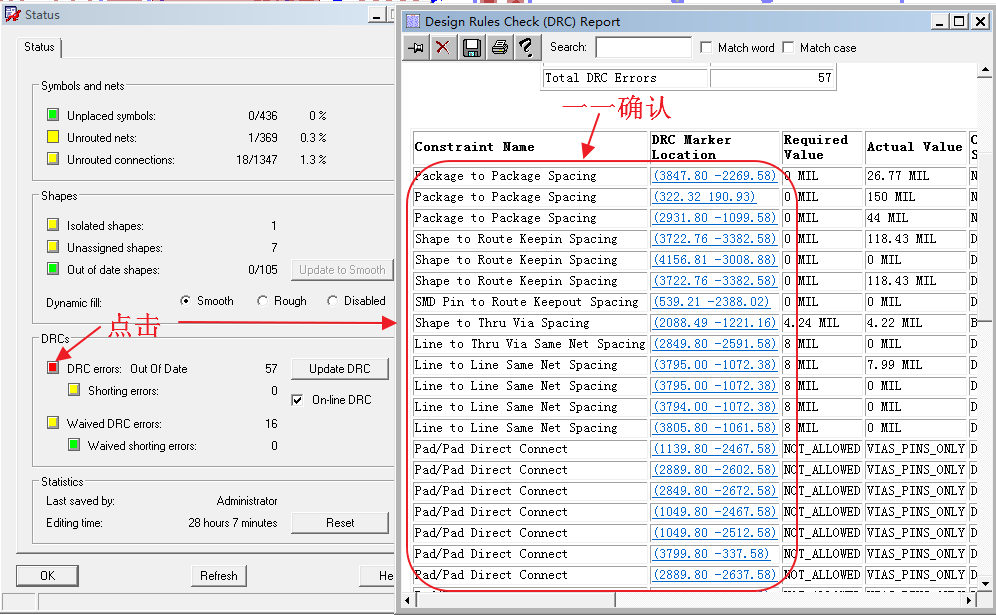

执行菜单命令“Display”→“Status”进入到Dispaly Statues检查界面,如图所示。

布线完成后,一定要检查Dispaly Statues里面的内容:

(1)器件和网络连通性:三个选项一定全部要为0,没有为0一定是有问题的;

(2)铜皮相关:Isolated shapes和out of date shapes一定要为0。Unassigned shapes有可能不为0,但是一定要确认其合理性,比如在板边加的工艺边有可能就是没有指定网络的铜皮,如图所示。

(3)DRC:DRC的部分原则上也要全部为0,但是也有一些合理的DRC,比如短路焊盘,打在热焊盘上的地过孔......如图所示。

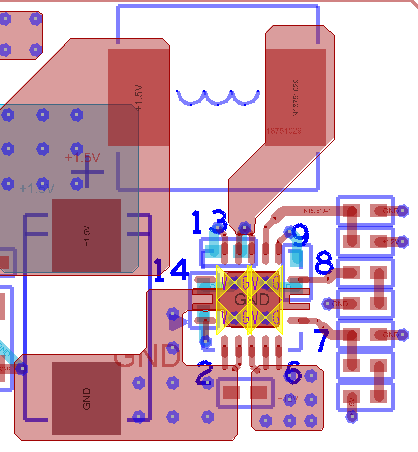

对于不为0的DRC一定要点开一一确认看它是否是合理的,如图所示。

对于Dispaly Statues里面的内容,只要是不为0的项,我们都可以通过上图所示的操作方法,点开其前面的矩形按钮,在随后跳出的报告窗口中通过坐标找到其相应的位置加以确认和解决。

3 Dangling Lines、 Dangling Via 的检查

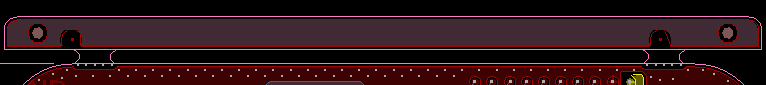

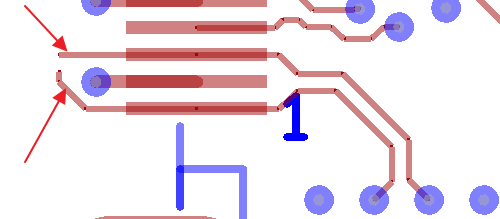

Dangling Lines是无用的走线,没有删掉的话就会成为板上的stub,如图所示。

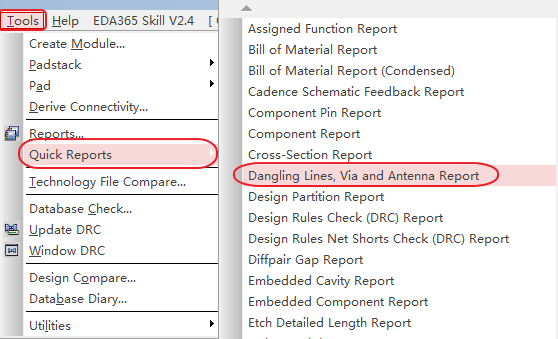

Dangling Via是板上不起任何连接作用的无用过孔,布线完成后一定要检查是否有这类过孔在板上,有的话一定要删掉。其操作步骤如下:

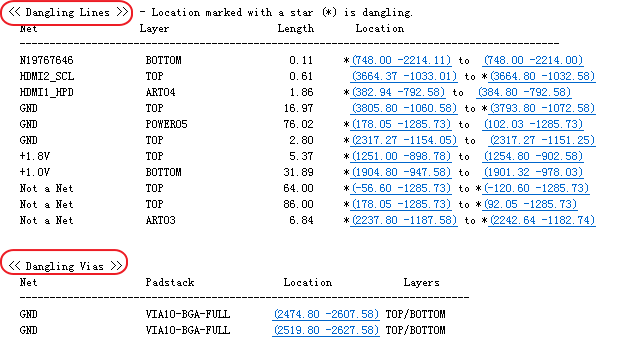

就可以打开Dangling Lines、 Dangling Via 报表,通过报表提供的坐标找到它然后将其删掉,如图所示。

4 单点网络的检查

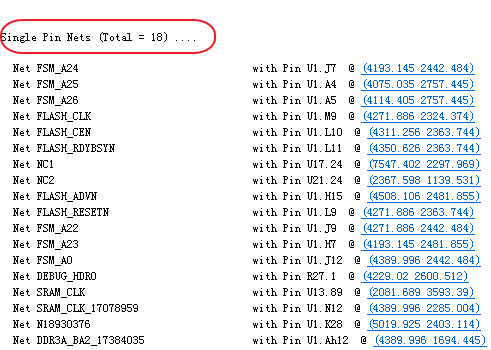

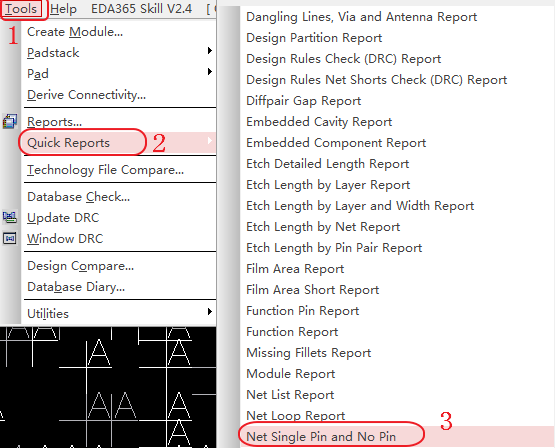

理论上一个网络至少要有两个连接点才能构成一个传输链路。只有一个点的网络,要么是设计原理图的时候特意为之,要么就可能是设计时的失误,PCB设计完成之后一定要输出出来做确认。执行如图所示的操作

可以输出单点网络报告,如图所示。