1.原理图生成网表

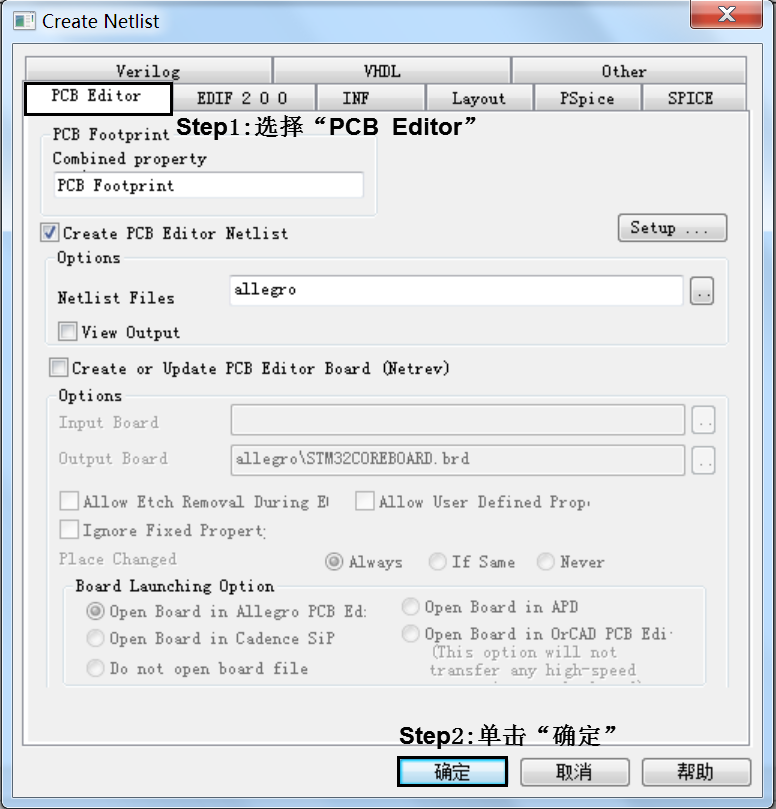

首先,在原理图设计系统环境中,对原理图进行检查,确保没有错误的情况下,选中原理图的.dsn部分,执行菜单命令“Tool”→“Create Netlist”命令,弹出“Create Netlist”对话框,在窗口中选择“PCB Editor”选项卡,直接点击“ok”,软件即可自动生成网表,如图所示。

、

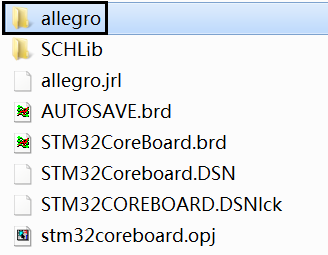

、在“PCB Editor”选项卡中“Netlist Files”文本框可以更改网表路径,这个路径可以不用设置,软件会自动在“DSN”同级目录下自动创建一个“allegro”的文件夹存放网表,如图所示。每次重新导出网表,该文件夹内文件都会被新的网表文件覆盖。

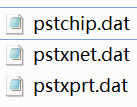

Allegro文件夹中存放的网表包含三个文件:“pstxnet.dat”、“pstxprt.dat”、“pstchip.dat,如图所示。

pstxnet.dat:定义各个器件引脚的电器连接关系;

pstxprt.dat:定义各个器件对应的封装类型 ;

pstchip.dat:定义各个封装的的相关参数;

pstxprt.dat,Pstchip.dat是两个独立的文件,它们是通过Pstxnet.dat进行关联。这三个文件共同组成allegro的网表文件。

2 网表调入

在网表导入前,需要告知软件从哪里获取元件的封装信息,就必须指定封装库路径,以便网表导入后能成功的把器件放到PCB设计工程图中。

需要设置的路径有devpath、padpath,psmpath 。

devpath是定义寻找Device文件的目录路径,主要用于第三方网表文件调入。

Padpath是定义寻找Padstack(焊盘)文件的目录路径。

Psmpath是定义寻找Symbol文件的目录路径。

操作步骤如下:

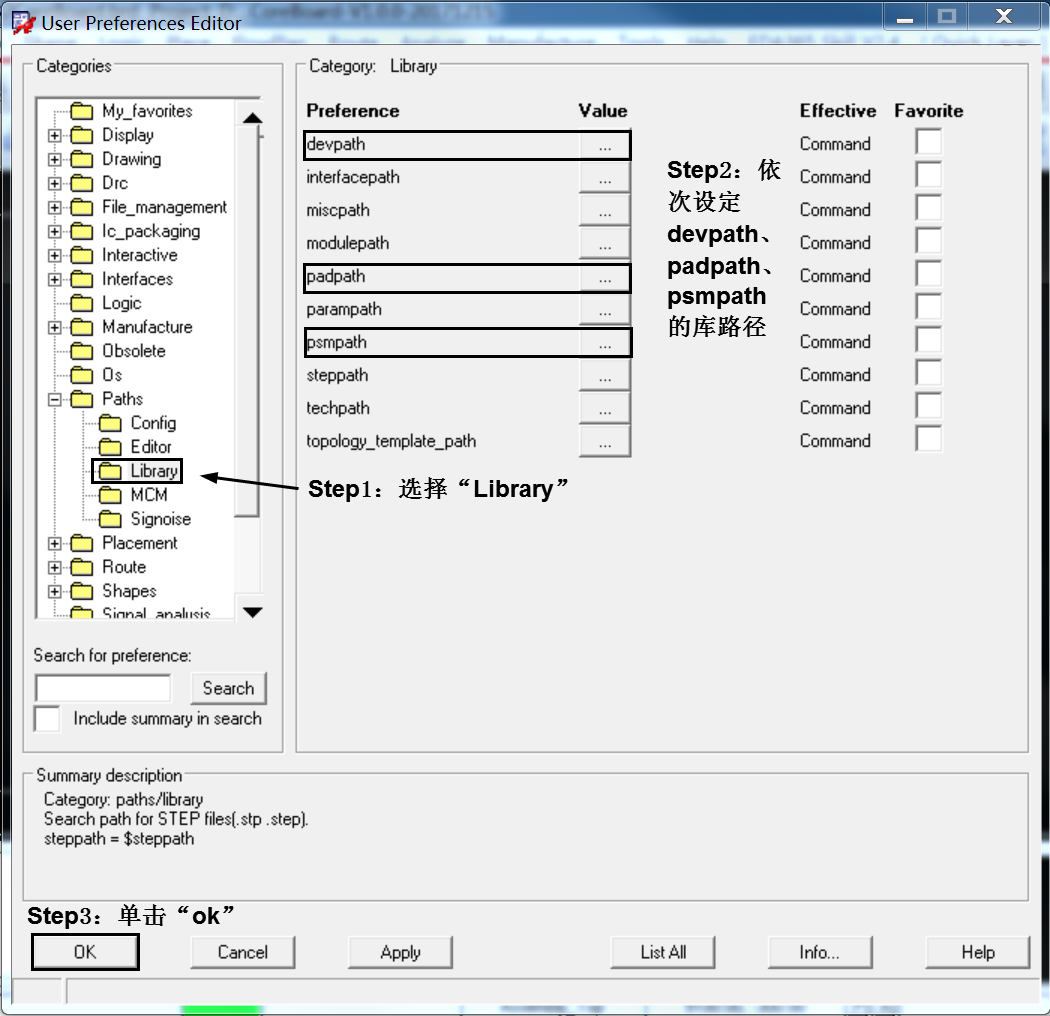

(1)执行菜单命令“Setup”→“User Preferences”命令后弹出“User Preferences Editor”对话框;

(2)在User Preferences Editor对话框中的Paths选项下选择Library;

(3)根据实际库文件的位置,分别指定devpath、padpath、psmpath的路径。如图所示。

库路径设置好后,就可以导入网表了。操作步骤如下:

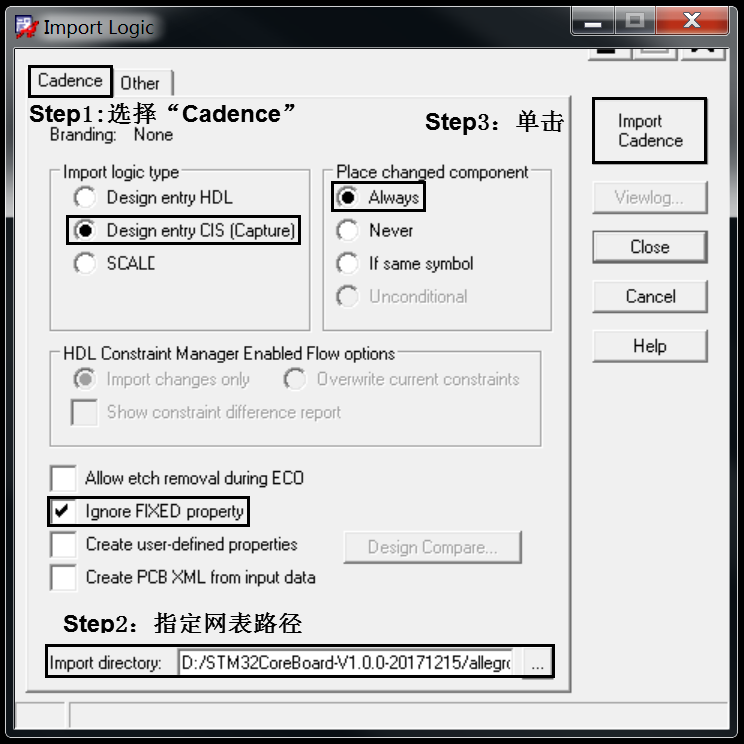

(1)执行菜单命令“File”→“import”→“logic”命令,弹出Import Logic对话框;

(2)选择Cadence选项卡,勾选如图所示的选项;

(3)在“Import directory”对应的文本框中指定网表路径,然后单击“Import Cadence”,软件即可自动执行导入网表操作。

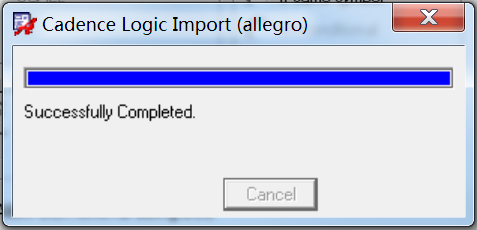

如果网表导入成功,会出现如图所示的提示框。

3.放置器件

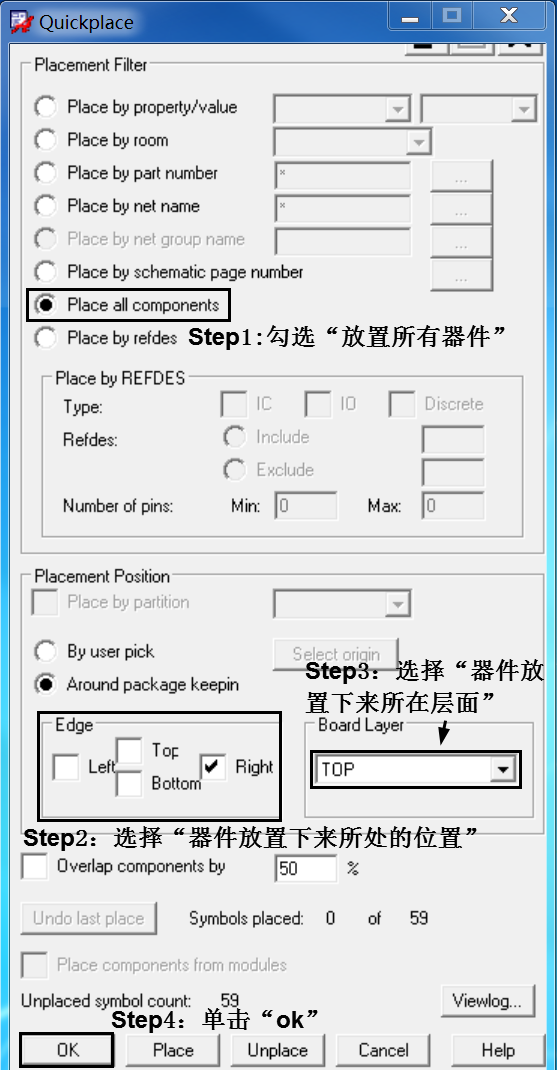

网表成功导入后,设计窗口还看不到器件,需要我们手动将器件放置到工程窗口中,单击菜单栏“Place”→“Quickplace”,进入快速放置元件窗口,勾选如图所示选项,单击“ok”,即可将所有器件放置下来。

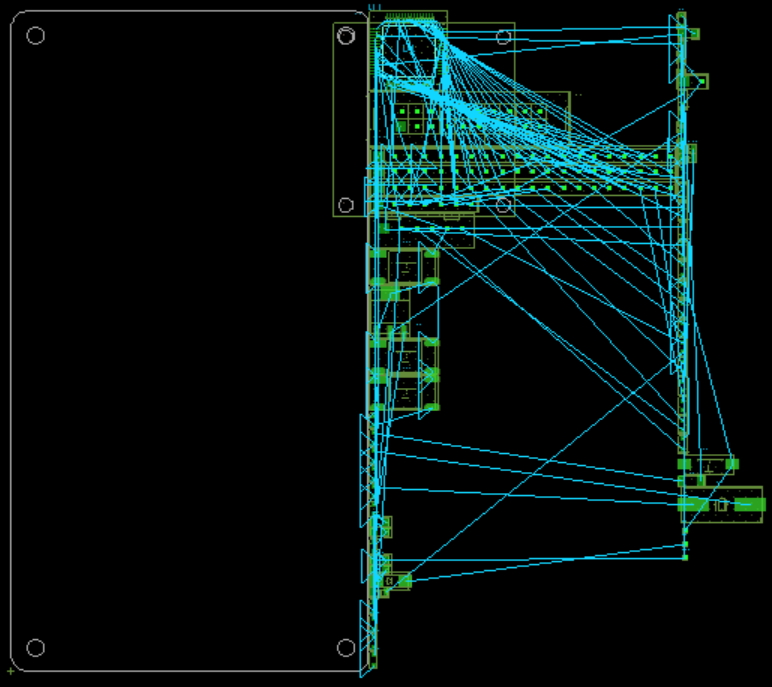

放置下来的器件如图所示。