背钻(Backdrill)就是通过控深钻孔,采用二次钻孔的方式钻掉过孔或通孔多余的残端,从而消除残端带来的寄生电容效应,保证过孔或通孔处与走线阻抗一致,从而减少信号反射,提高信号完整性,改善信号质量。背钻是目前性价比最高、提高信道传输性能最有效的生产技术,因二次钻孔会使PCB制造成本有一定的增加。

Allegro支持背钻工艺,并提供了输出背钻所需生产文件的功能,具体步骤如下。

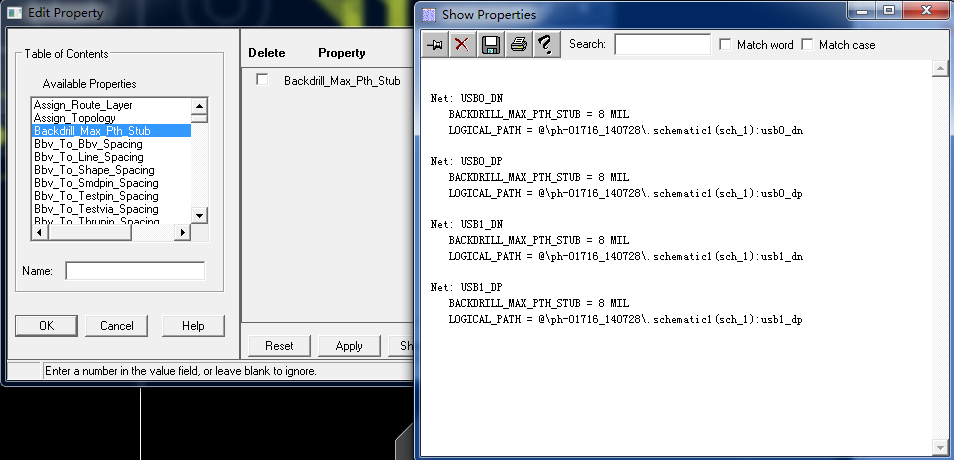

(1)执行菜单命令“Edit”→“Properties”,Find面板中仅勾选Net,从PCB上选择需要背钻的信号,添加Backdrill_Max_Pth_Stub属性,数值为板厂背钻剩余残端最大长度,通常为8mil。在执行菜单命令后,可以用鼠标右键的Temp Group命令选择多条信号,选完信号后再单击Complete按钮设置该属性,如图所示。

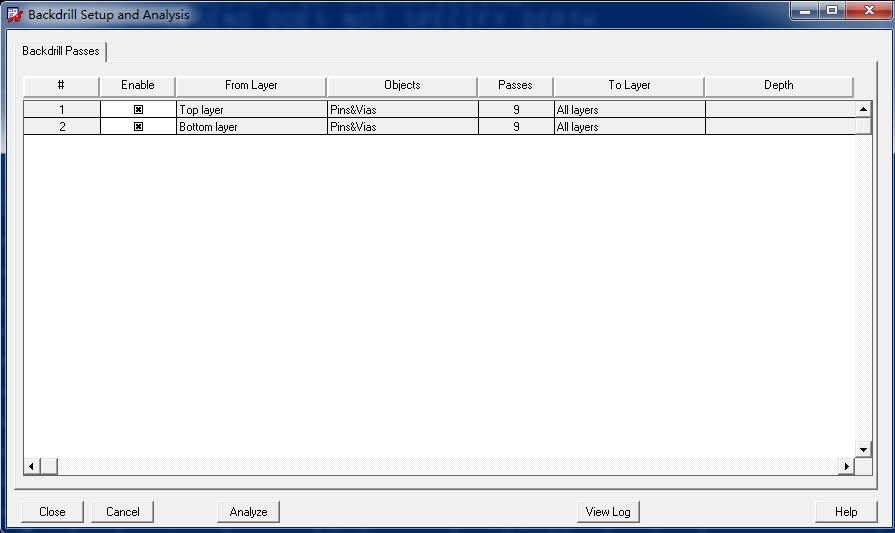

(2)设置背钻起止层,执行菜单命令“Manufacture”→“NC”→“Backdrill Setup and Analysis”,在弹出的对话框中选择起始层,一般会有两种,从Top层开始钻或者从Bottom层开始钻。如果连接器在Bottom层,通孔需要从Top层背钻;如果走线是从Top层打孔到ART03层需要从Bottom背钻,如图所示。

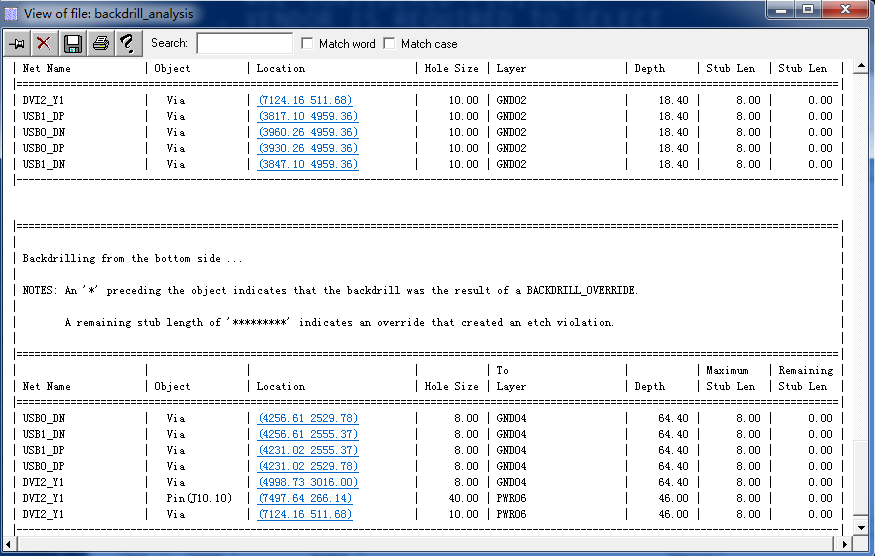

(3)单击上图所示的Analyze按钮后,将报告背钻生成情况,报告内容如图所示。

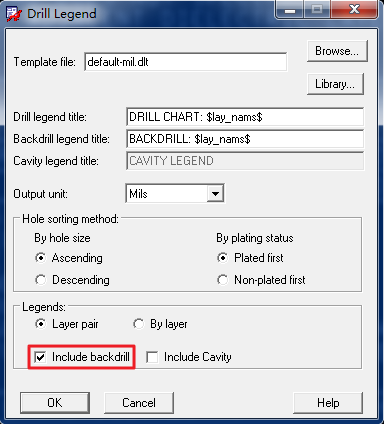

(4)在提取钻孔表格时,需勾选Include backdrill选项,如图所示

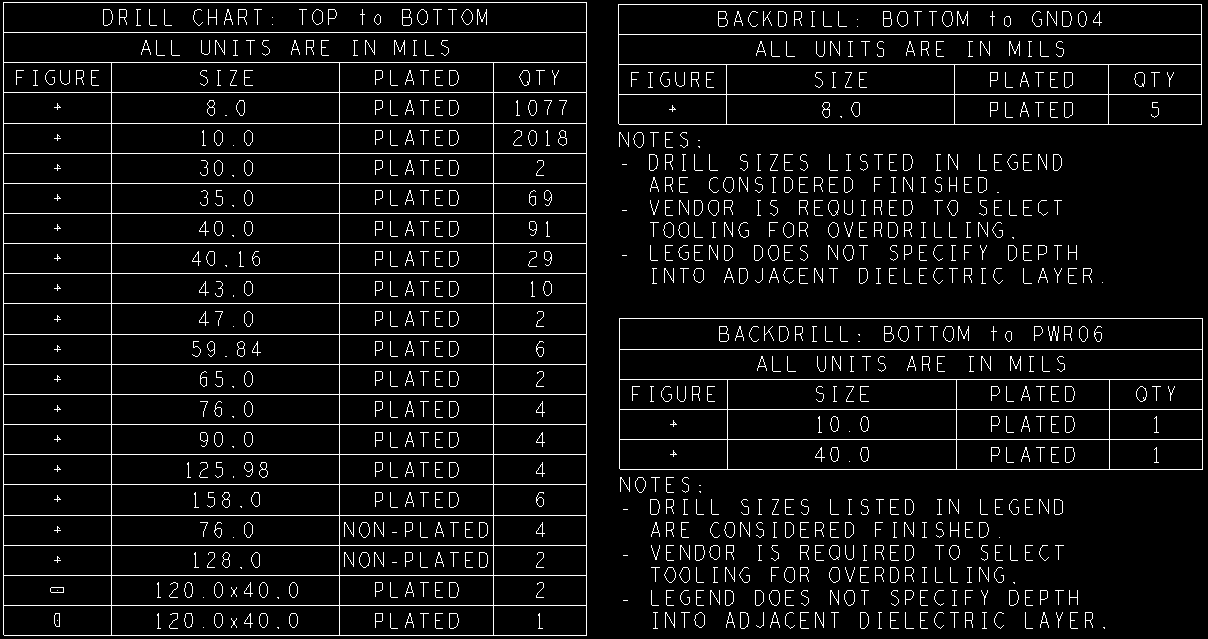

生成的钻孔表格如图所示

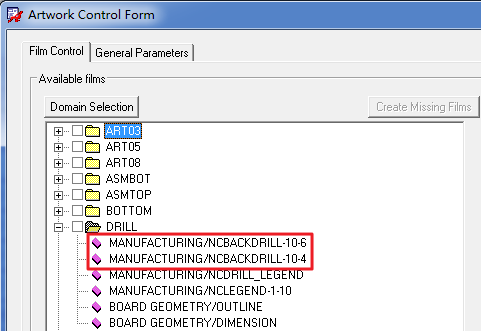

在Gerber设置中将背钻符号所在层加入Drill的Gerber中,如图所示

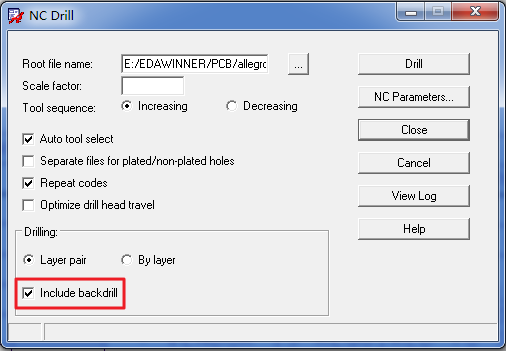

输出钻带文件时需勾选Include Backdrill复选框,如图所示

(7)最后要将输出的被钻文件与生产文件一起打包发给板厂。

注意背钻时应用比当前孔径至少大一号的钻针,因此背钻孔周围的走线、过孔、铜箔要比正常的间距大一些,建议间距在10mil以上。