原理图画好后,要将原理图中的元件参考编号、元件封装、网络名、网络连接关系等等信息导入到EDA工具中开始PCB板的设计,

而网络表就是包含所有这些信息的一个文件。

下面介绍PADS Logic如何同步网表到PADS Layout

用PADS Logic绘制的原理图可以将网表直接同步到在PADS Layout。

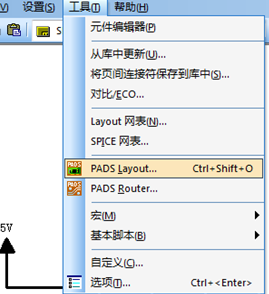

第一步,在PADS Logic中,执行工具>PADS LAYOUT LINK

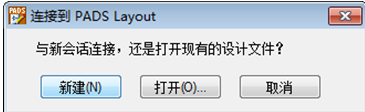

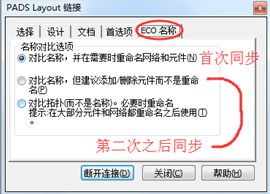

弹出「PADS Layout 链接」的窗口,如图所示。

在随后弹出的对话框中选择:新建

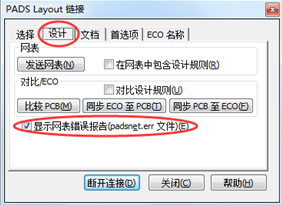

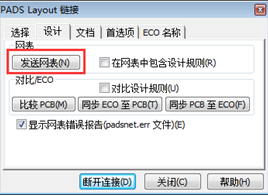

“设计”标签中,设置如图所示。

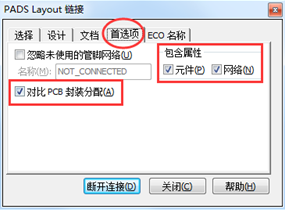

“首选项”标签中,设置如图所示。

“ECO名称”标签中,设置如图所示。

确认设置正确后,单击“设计”选项标签,单击”发送网表”按钮,如图所示。

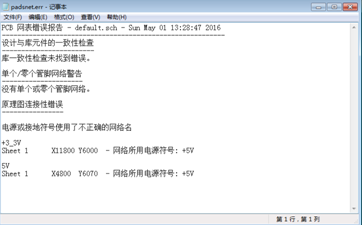

此时可能会弹出网表错误报告,如图所示。

“电源或接地符号使用了不正确的网络名”,这个错误可以忽略。

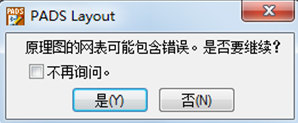

确认没有错误后,关闭报告,会有窗口询问是否继续,点击“是”继续。

此时软件后台在PADS安装目录下的PADS Projects文件夹下会自动生成如图所示的原理图网表。

设计所需的所有PCB封装就会出现在新建的PADS Layout中,并附着在原点上,如图所示。

此时PADS Logic原理图的网表就成功导入到PADS Layout中。

==============================================================================

配套的教学视频见这里:www.580eda.net 在首页找:PADS Logic如何同步网表到PADS Layout