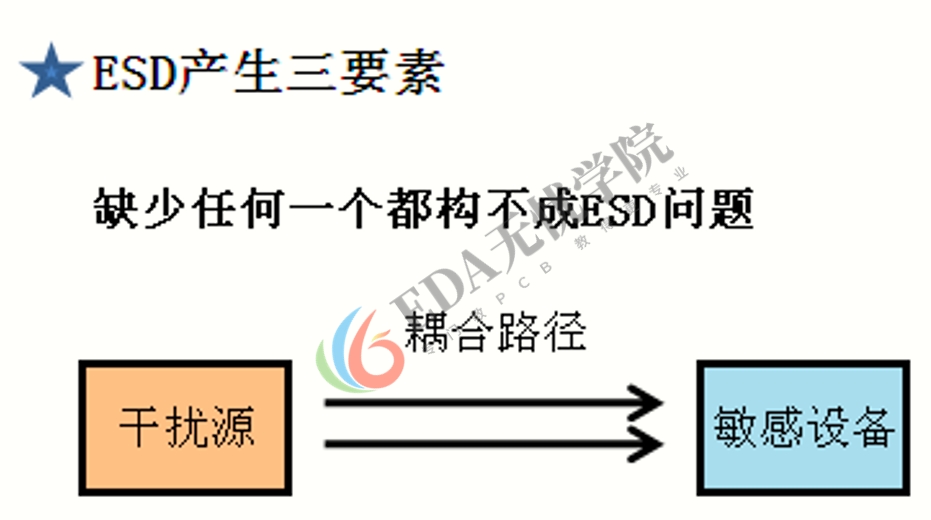

一、ESD产生要素

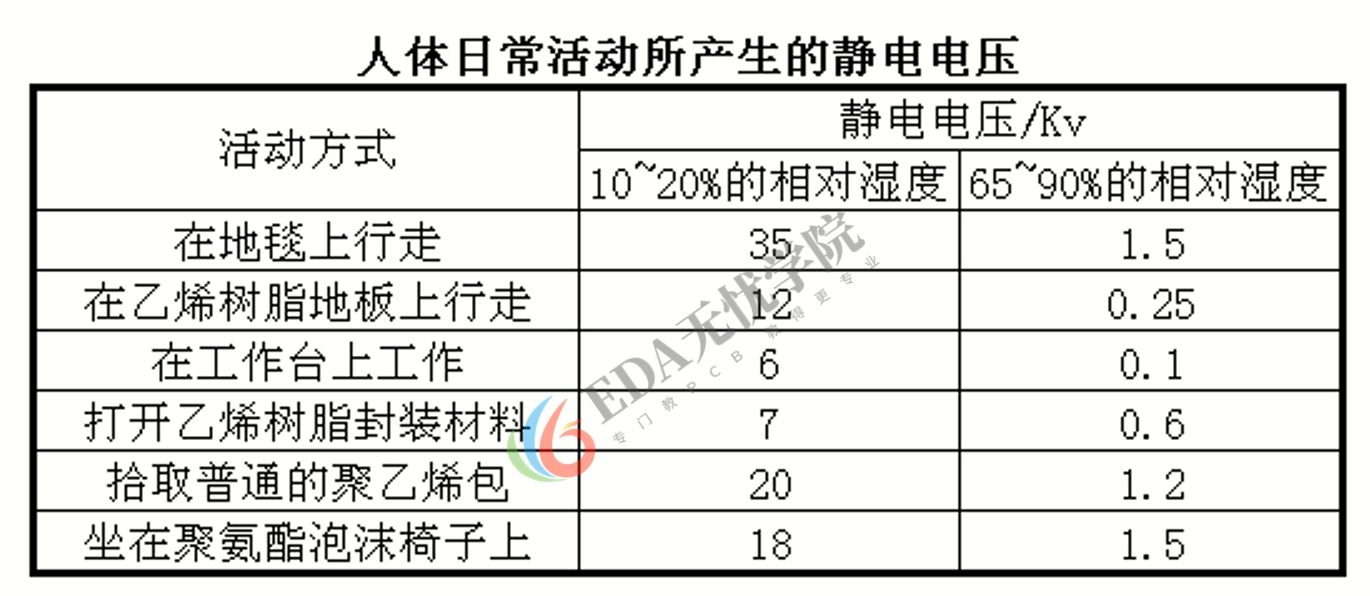

ESD是本世纪中期以来形成的以研究静电的产生、危害及静电防护等的学科。因此,国际上习惯将用于静电防护的器材统称为“ESD”,中文名称为静电阻抗器。

ESD是困扰许多电子产品的一个严重的问题。在PCB设计初期就必须考虑ESD的防护问题。

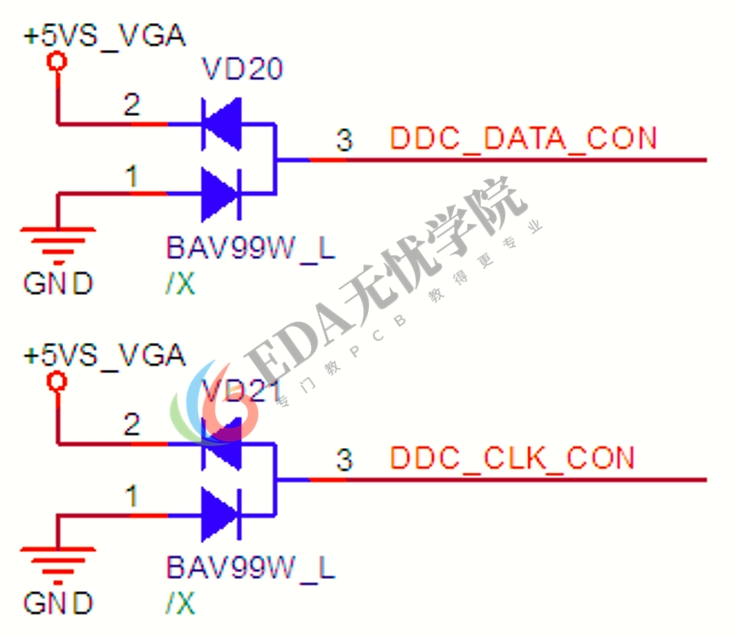

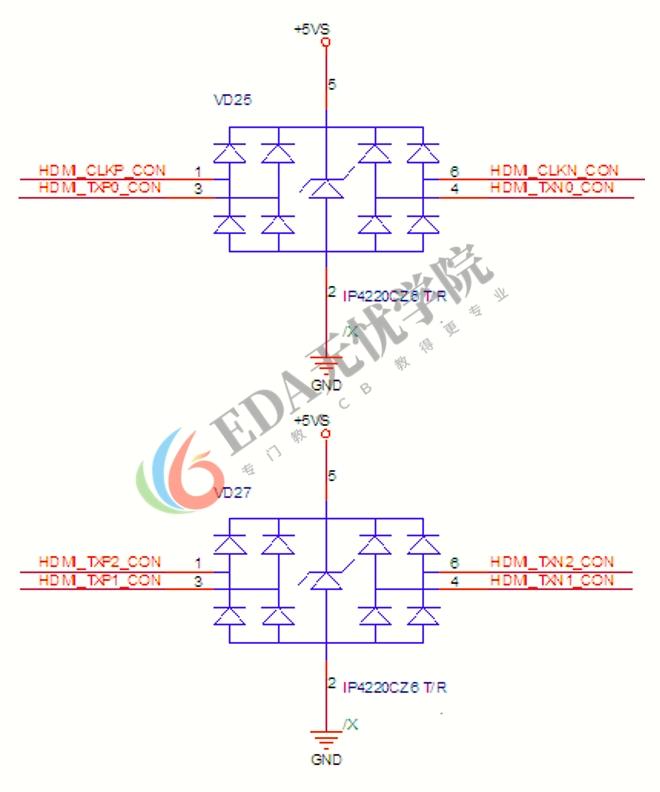

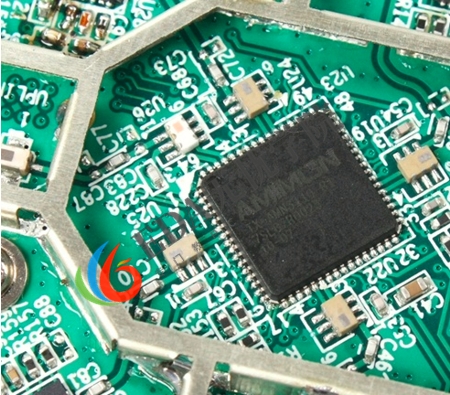

二、常用ESD保护器件和电路

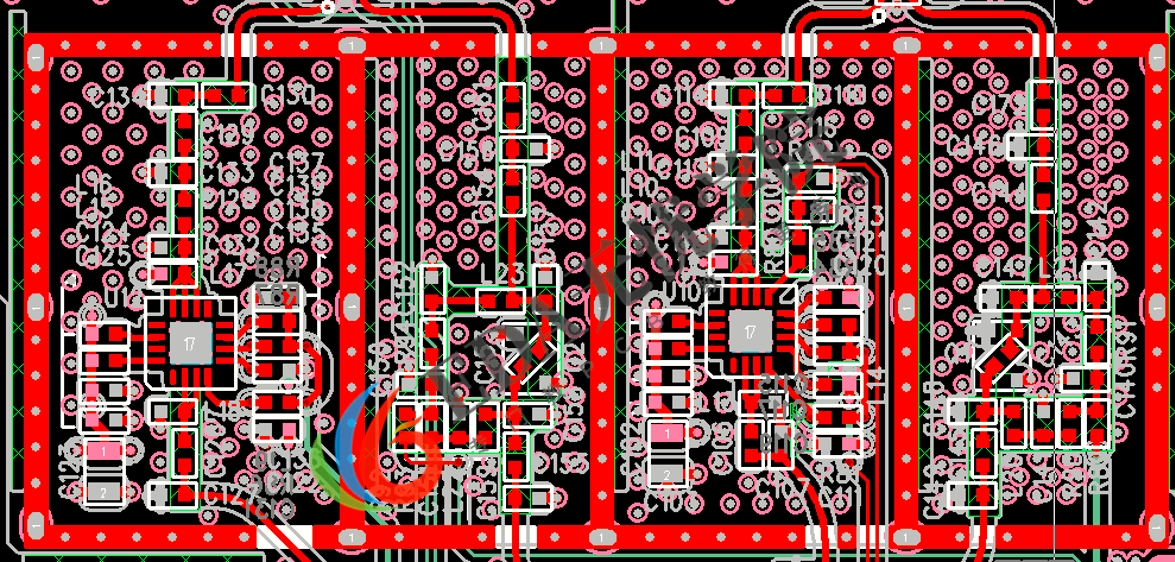

三、ESD防护Layout原则

布局原则:

- 尽可能将ESD保护器件靠近输入端或者连接器

- ESD保护器件与被保护线之间的线路距离应该尽量短

ESD防护设计-低速板:

- 横平竖直走线,尽量减少信号线路并排走线

- 空间允许的话,走线越粗越好

- 按高速电路设计理念来进行布线

- 避免在PCB边缘处理重要的信号线,如时钟、复位信号等

- 所有PCB板的传导环路包括电源和地线环路应该尽量小

- 如果没有使用电源平面的话(单面或双面板),则电源走线旁边必须要跟随一根地线。(布线顺序是:电源模块→电源走线→地线→信号线)

- 尽量使用多层板

ESD防护设计-高速板:

- 要有良好的地平面

- 保持足够的间距:如滤波器,光耦,交流电源线与弱信号线

- 长距离走线加低通滤波器(C,ESD器件,RC,LC)

- 隔离(增加屏蔽罩),避免被保护的导线与未被保护的导线并排走线。

- 避免与其他器件使用同一条回路来连接公共接地点

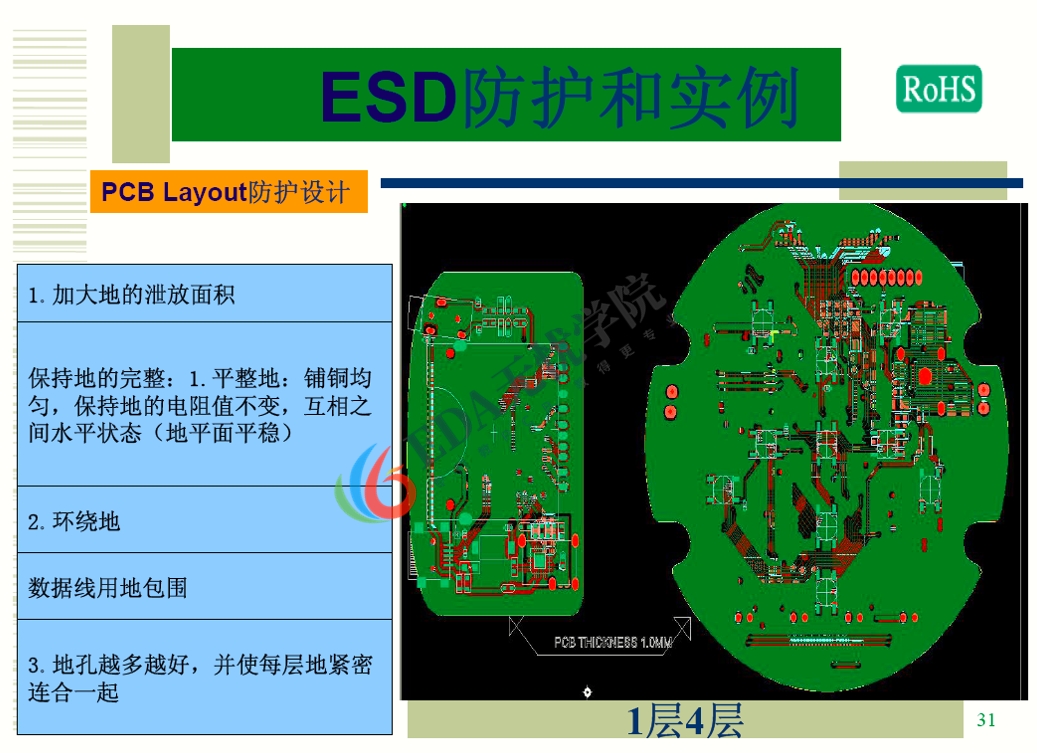

四、ESD防护和实例

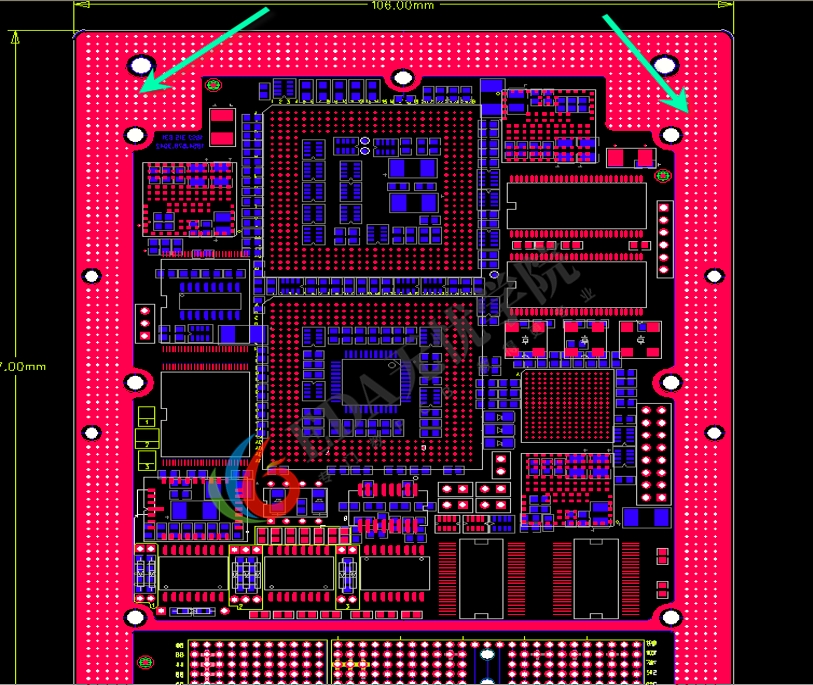

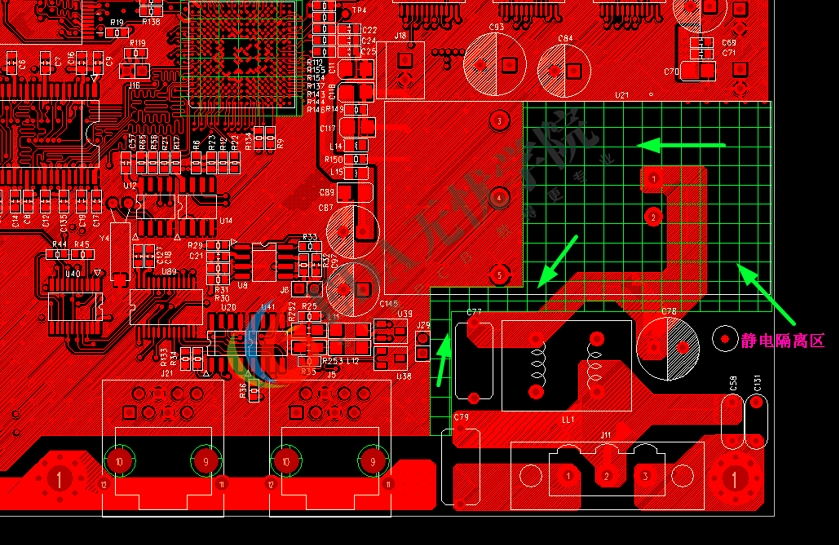

对于PCB设计来说,在容易发生静电放电的边缘设置一定的隔离距离非常重要。一般认为,对于机架类产品,每千伏的静电电压的击穿距离在1mm左右。如果在容易放电的边缘设置一个3~5mm隔离区,就可以抵抗3~5kV的静电电压。

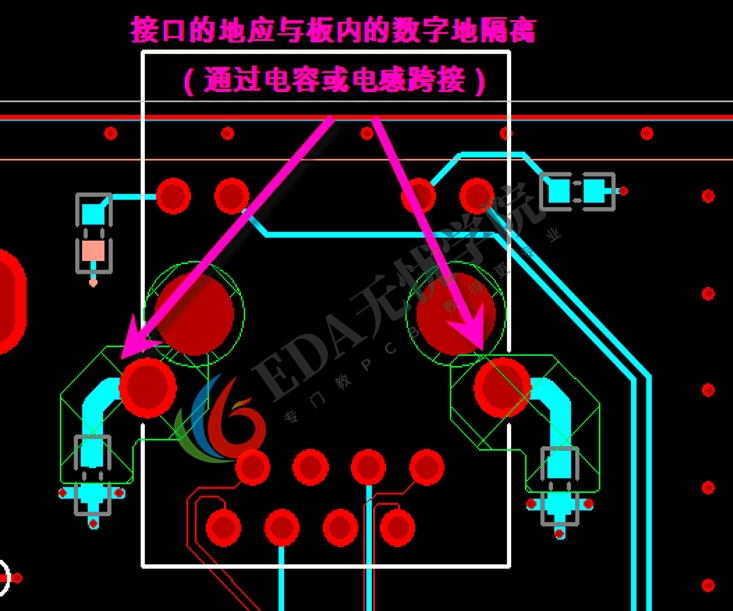

在PCB上安装光耦合器或者变压器,以及结合介质隔离和屏蔽都可以很好的抑制静电放电冲击。

可将PCB的GND与外壳地进行单点接地,防止静电放电电流在机箱上产生的电压耦合进电路。(需注意接地点的选择:选择在电缆入口处)

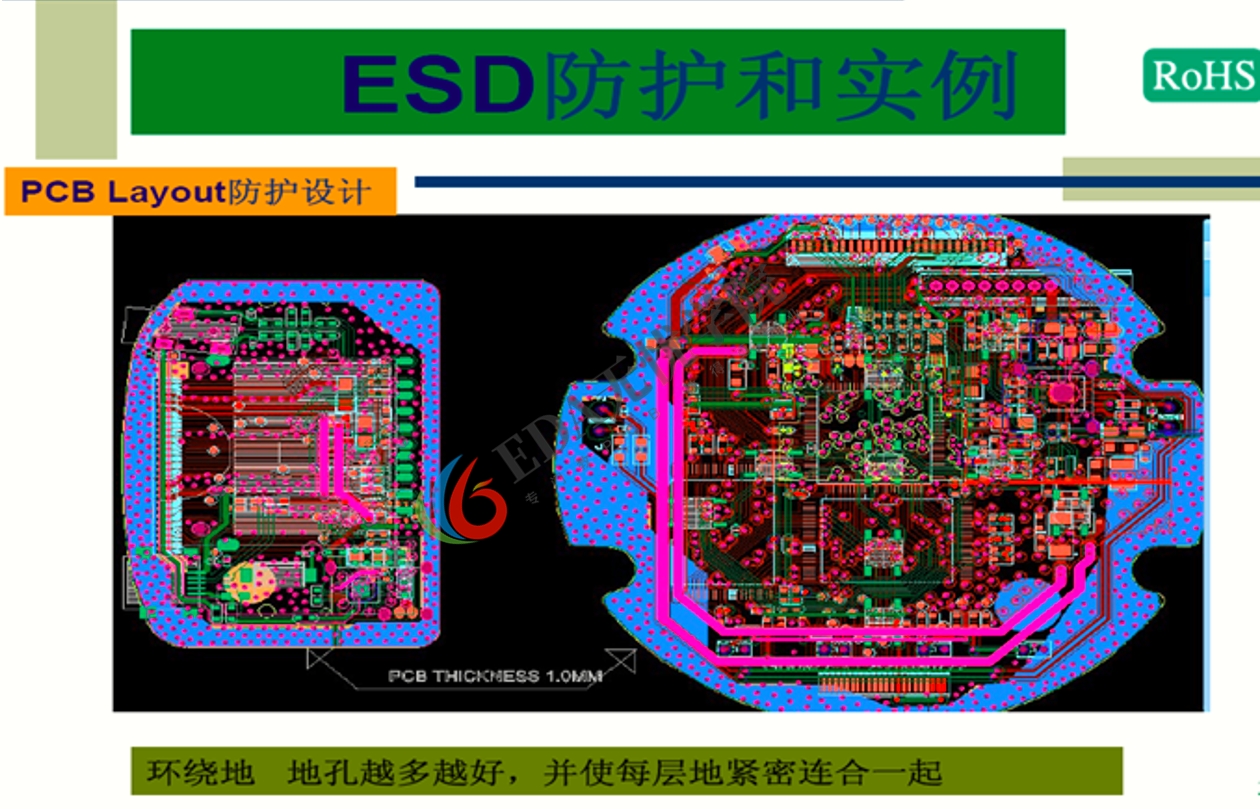

如果PCB面积允许,并且整机系统的搭接、静电泄放通道都很好,可以在PCB周围设置接地防护环(可裸铜处理),并采用很多通孔连接。