PCIE (PCI Express接口)

PCIE属于高速串行点对点双通道高带宽传输,所连接的设备分配独享通道带宽,不共享资源,主要支持主动电源管理,错误报告,端对端的可靠性传输,热插拔以及服务质量(QOS)等功能。

一、PCIE接口Layout要求

PCIE接口可以全面取代PCI和AGP, 数据传输速率最高可达10GB/s以上。

1、差分阻抗:85 或 90 ohm(+/-10%)

2、走线长度控制在1-12英寸

3、差分对内等长误差为5mil,两组差分线之

间的间距>=15mil,与其他信号或灌铜也应

保证间距>=15mil

4、尽量不打过孔或将过孔数量控制在2个以内

5、TX和RX信号分别走在同一层面,要完整的参考平面,优先邻近GND层走线

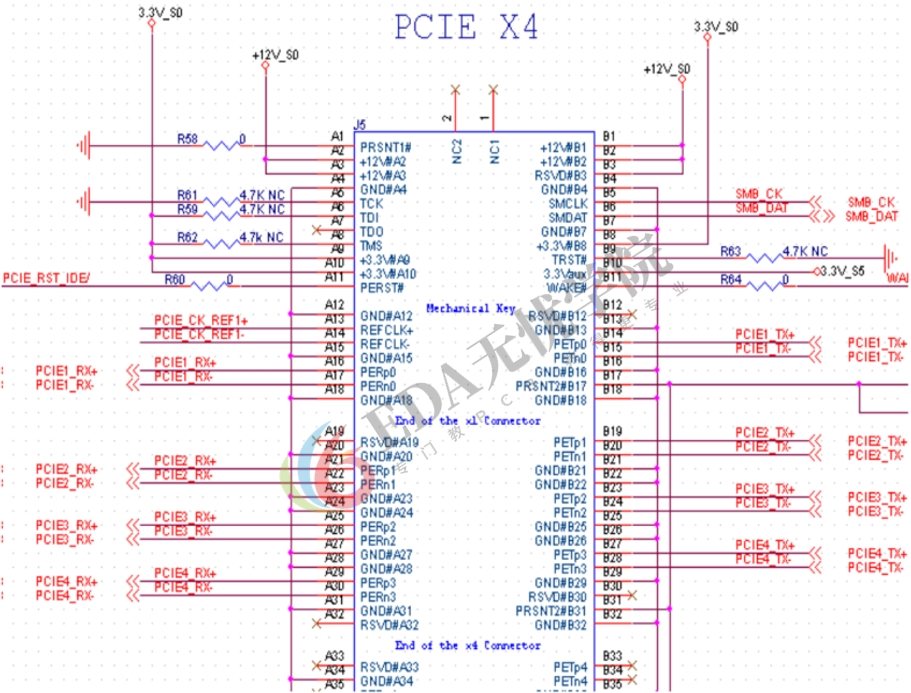

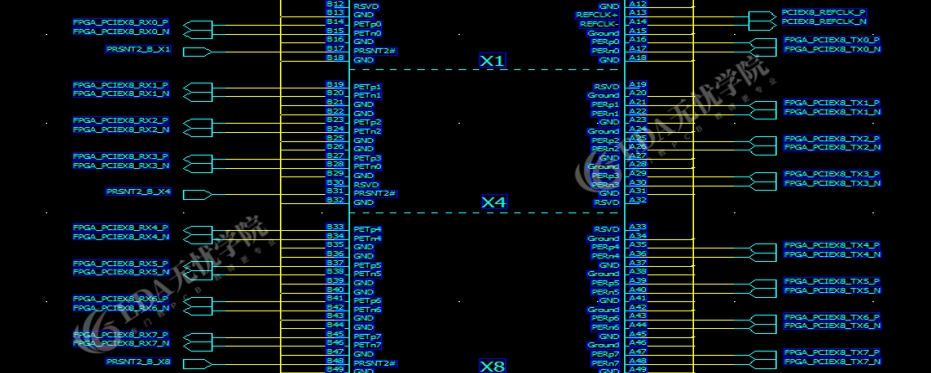

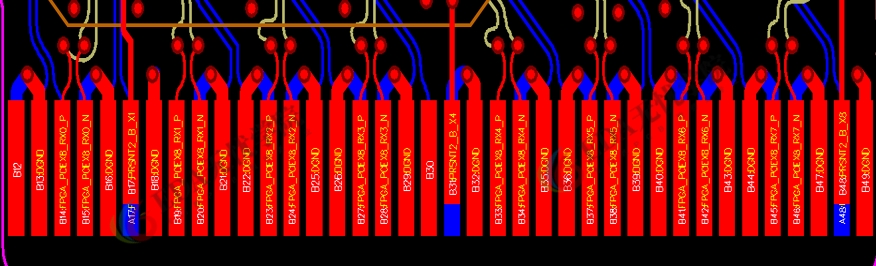

二、PCIE实例设计

PCIE (M.2接口)

一、PCIE Lines布线指导

在布局布线过程,按以下规则指导以确保最佳信号质量和尽量减少反射。

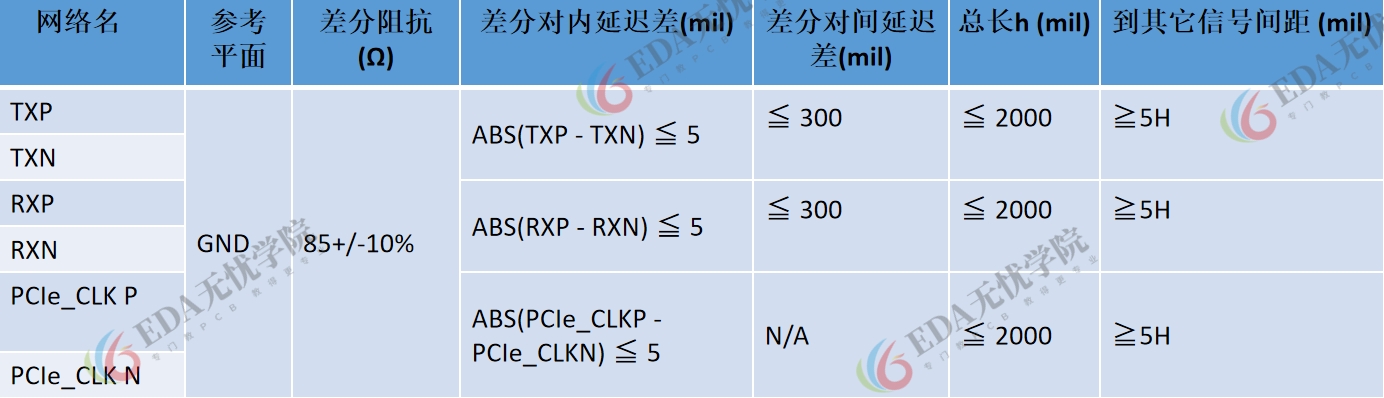

二、TX\RX差分线布线要求

- TX和RX之间不要求做等长,但TX和RX各自对内需要做等长,对内误差为5mil。

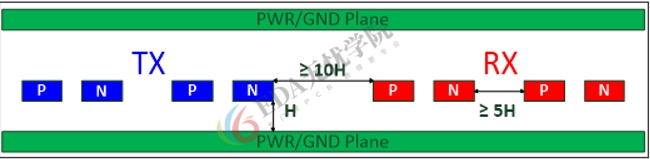

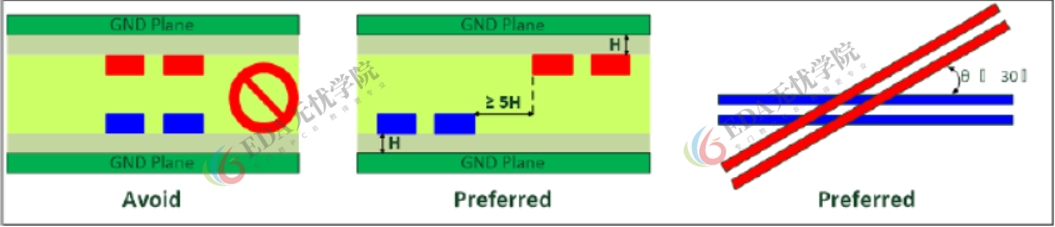

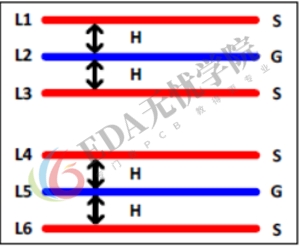

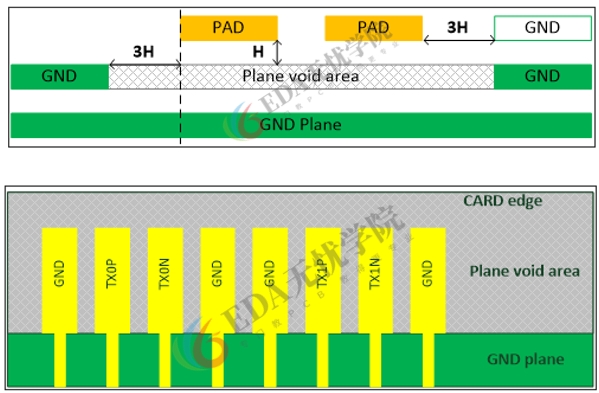

- H为TRACE到最近参考平面的距离。

- 对其他信号包括其他接口的间距要>5H,如SDRAM, NAND, POWER等。

三、PCIE(M.2)布线规则

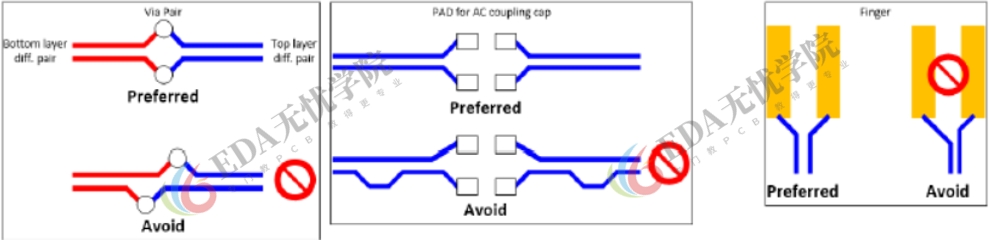

◼ 差分对内(P 和N)的长度误差控制在5mil以内

◼ 不要计算FINGER-PAD 内部的布线长度

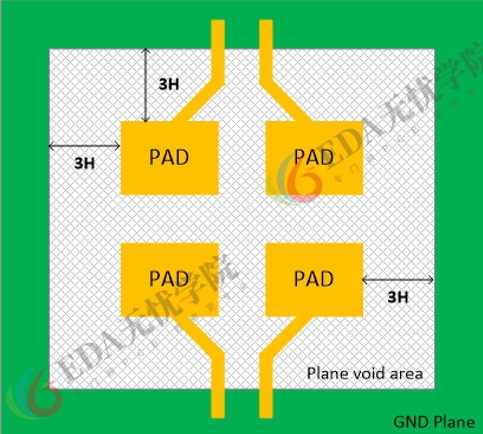

◼ TRACE/VIA/FINGER-PAD/电容- pad 采用对称布线

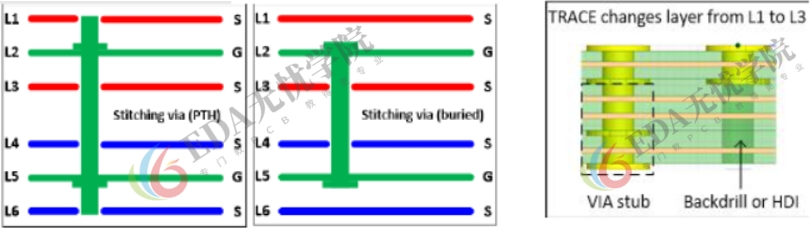

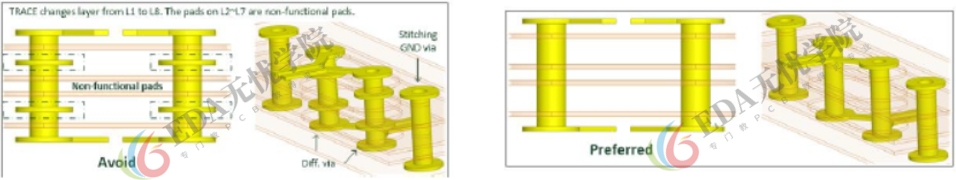

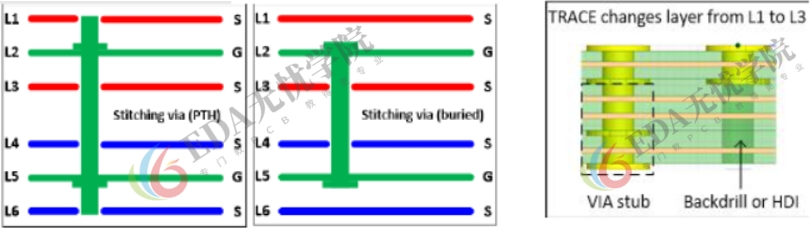

◼ TRACE 改变层时,对称添加拼接VIA,并靠近信号VIA,以避免参考平面不连续。

◼ 如果TRACE 更改层后参考平面相同,则无需添加拼接via。

例如TRACE 将L1 层改为L3 层。 参考平面仍然是L2。

◼ 最小化TX/RX/CLK TRACE 上的VIA 数量。

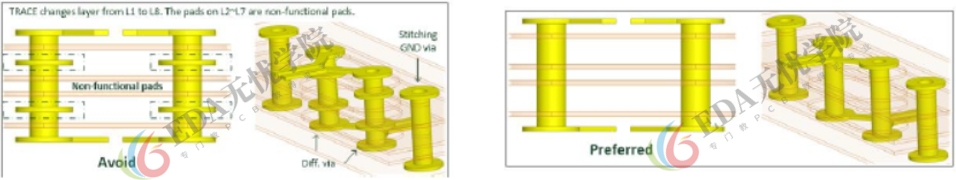

◼ 从内部层去除非功能性焊盘,以减少通过电容产生的过剩。

◼ 根据不同的堆叠方式,VIA/BALL-PAD/FINGER-PAD/CAPACITOR-PAD可能需要进行微调以匹配TRACE阻抗。

◼ 如果有测试点,测试点的Stub尽可能短,测试点的焊盘尽量小。

◼ 保持VIA残留根尽可能短。 TRACE从顶层到底层时,VIA残留根比L1到L3短。

◼ VIA残留根可以通过从顶层到底层布线到2层(背钻)。

◼ 将交流耦合电容靠近FINGER。

◼ 使用小封装的交流耦合电容器,如0201。 220 NF建议。

◼ 优先考虑非交错布线(RX组/CLK在同一内层,TX组在同一内层)。

◼ 如果TX和RX路由在同一层,则要求TX和RX之间的间距大于10H。

◼ 带状线优先。 优先走在内层。