大电流的载流能力是电源地设计考虑的重点,尤其是在当前的高速PCB设计中,随着电压降低和功耗增大,板上承载的电流越来越大,一些Core电压的电流甚至达到或者超过100安培。需要在PCB设计上考虑这么大的电流的载流能力和由此引起的电压跌落、温升等问题,是比较有挑战性的。

每个芯片工作时都要消耗一定的能量,这些能量的供给通道就是PCB上的走线,影响到PCB上走线载流能力的几个关键因素有线宽、铜厚、温升、层面。

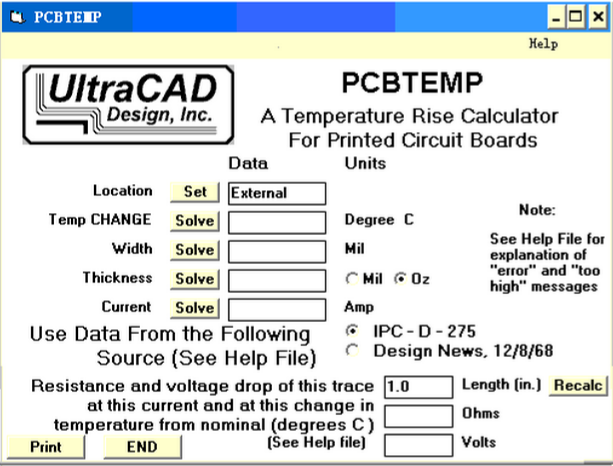

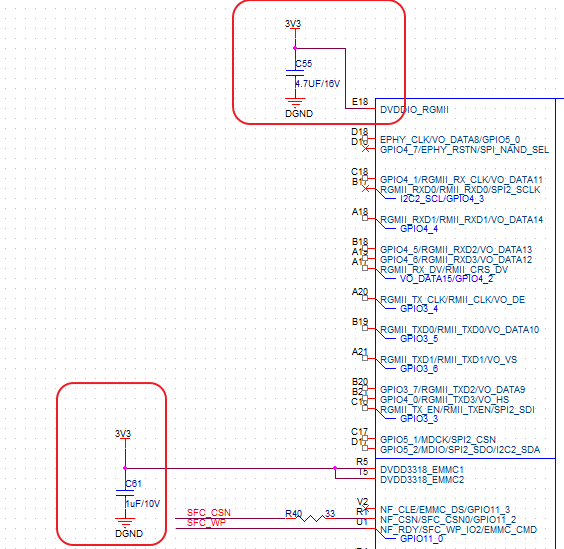

(1)线宽:即电源走线的宽度,如果是铺铜来实现,则考虑铜皮的最细处的宽度,同时要减去最细处其它网络过孔的避让宽度(这是简单计算时的处理方式,严格来说,有其他网络过孔的避让铜皮,不能用简单的减法来计算有效通道,因为铜皮的宽度和载流能力之间不是线性比例关系。这个时候,PI仿真的IR Drop的功能可以帮助工程师准确得到铜皮的载流能力和压降数据)。长距离布线时,需再增加50%的裕量,保证PCB印制线不被熔断或烧损。符合载流能力的布线参数可以通过PCBTEMP软件来进行计算,如图所示。

① Location:选择内层铜箔,还是外层铜箔。

② Temp CHANGE:铜箔的最大允许温升,根据PCB加工工艺及对板材的影响,一般取10℃。

③ Width:铜箔最小宽度(电源通道走线或者铺铜的宽度)

④ Thickness:铜箔厚度,有两种单位:mil和Oz,它们的换算关系如下:1Oz=1.4mil

⑤ Current:铜箔的最大允许通流能力

(1)铜厚:电源走线所在层的铜厚,常见内层(电源、走线混合层)为1oz。如果需要加到2oz及以上,最好把电源地层设计到一个芯板的两面。

(3)温升:允许因电源走线温度升高而导致整个PCB的温度升高的范围。

(4)层面:分为外层电源走线和内层电源走线,通常外层比内层载流量大。

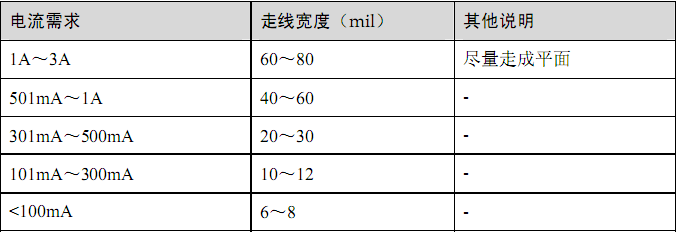

(5)在实际的设计当中我们还是要留够裕量,设计时我们应当遵循表11-1电流需求和走线宽度对应表(铜厚1oZ)

2电源通道和滤波

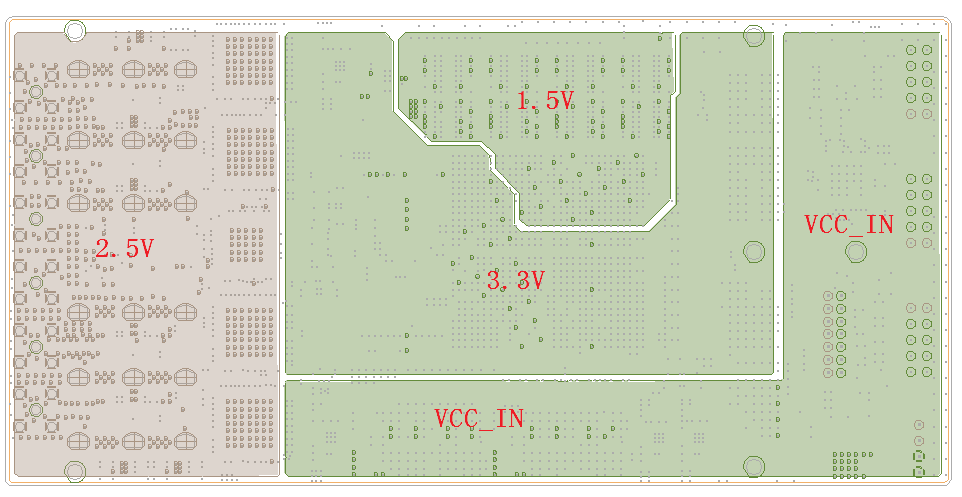

明晰每一个电源的来龙去脉才能够清楚整个单板的电源分布,在布局前对整板的电源树(图8-4)要有个直观的了解。每一种电源都会有它的主要电源通道,合理地设计整板的电源通道才是成功的关键。规划整板电源主要的几个原则如下。

(1)按照功能模块布局,电源流向明晰,避免输入、输出交叉布局。

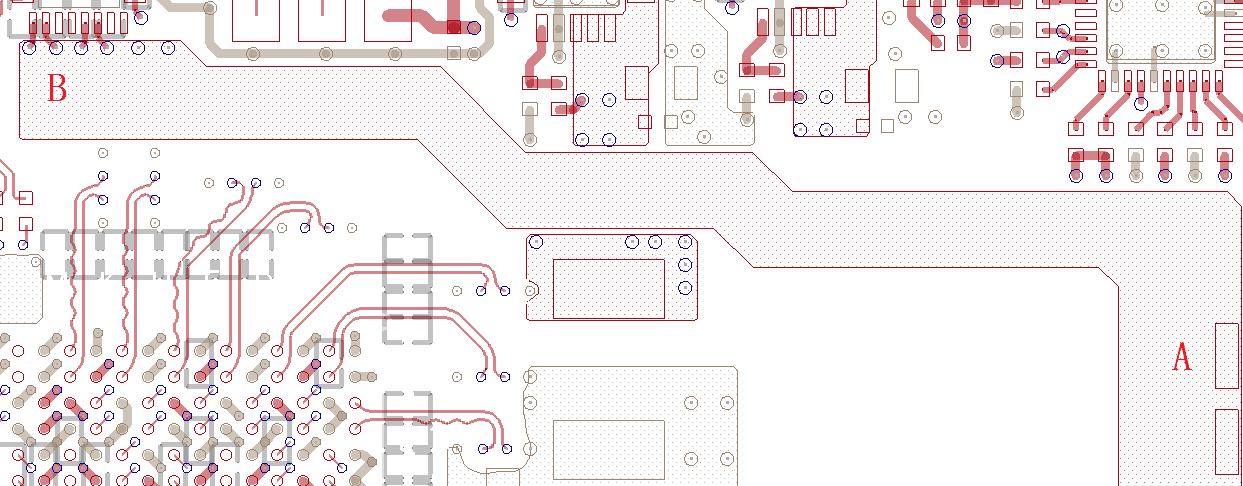

(2)各自功能模块相对集中、紧凑,避免交叉、错位,这样对电源有个清晰的规划和布局,在分割电源的时候就会比较得心应手节省设计时间,如图所示。

(3)整个电源通路布线(或铜箔)宽度满足载流能力要求:根据我们现在主流的设计经验,在温升10℃,铜厚1OZ的情况下,1mm(40mil)的线宽承载1A的电流。

(4)电源模块或电源芯片,必须在其输入端加滤波电容,并且在满足DFX前提下要将电容尽量靠近其电源输入端。其作用有以下3点:

①减小电源内部产生的反灌到输入侧的杂声电压。

②防止当模块输入端接线很长时,输入端产生输入电压振荡。这种振荡可能产生几倍于输入电压的电压尖峰,轻则使电源输入不稳定,重则会对模块造成致命损坏。

③如果模块输入端出现不正常的瞬态电压时,此电容的存在可抑制短暂的瞬态电压。

(5)电源模块或电源芯片,必须在输出端加滤波电容,并且在保证热设计前提下要将电容放置在靠近电源输出端。该电容有如下几个作用:

①减小输出纹波值。

②改善模块在负载变化时的动态性能。

③改善模块某些方面的性能(如启动波形、系统稳定性等)。

④模块输出关闭后输出电压可以维持一段时间以保证负载电路的某些操作能正常完成(如储存数据)。

(6)芯片端的滤波电容考虑:电容主要用于保证电压和电流的稳定。处理器的耗电量处于极不稳定的状态,可能突然增大,也可能突然减小,特别是在执行了一条待机指令,或者恢复至正常工作状态的时候。而对电压调节器来说,无论如何都不可能立即对这些变化做出响应。

对于一些功耗大、高频、高速的器件,其电源设计要求如下:

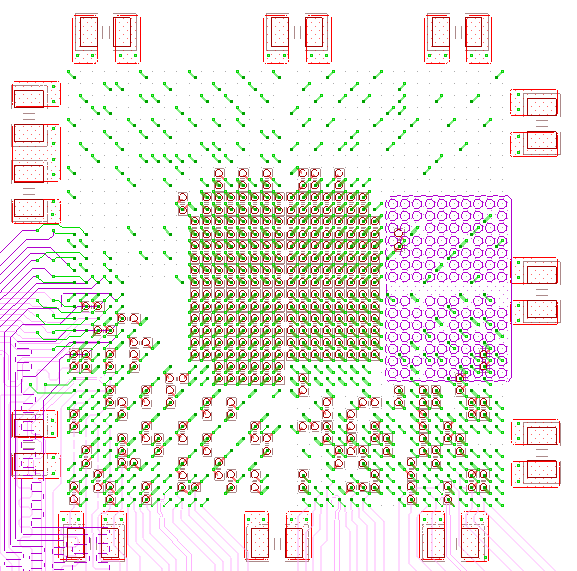

①在该芯片周围均匀放置几个储能电容,如图所示。

②对于芯片手册指定的电源引脚,必须就进放置滤波电容,对滤波无特殊需求的情况下,可酌情考虑防止适当的滤波电容。

③滤波电容靠近IC的电源引脚放置,位置、数量适当。

④对于一些特殊的芯片,需要考虑滤波电容的容值是否合理,以及不同容值应该对应哪些引脚设置。如图所示,同样是3.3V和0402封装大小的电容,但是他们的容值不同也对应了不同的引脚设置。

此外,还需注意整板电源滤波电容分布是否合理,数量是否足够。

3.直流压降

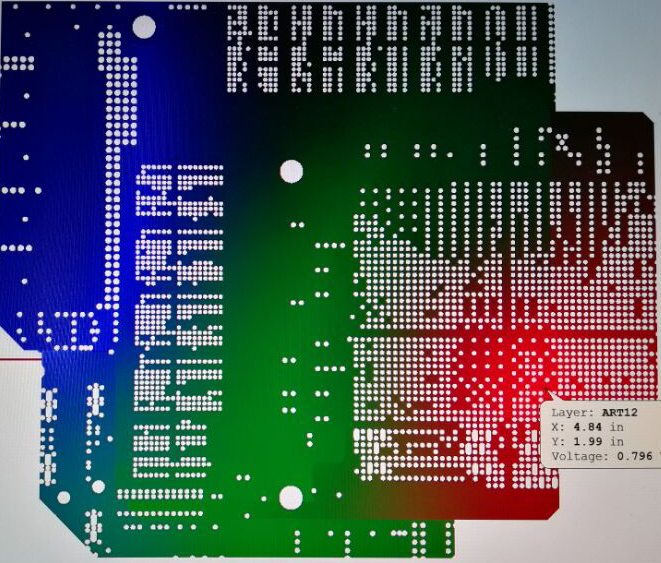

(1)压降:由于走线或铜皮本身都有一定的阻值,电流通过后会产生压降。如图所示

假如电源由A点输出向B点供电,由于从A点到B点这段铜皮是有一定阻值的,所以这段铜皮上会有直流压降,那么实际B点的电压,应该为:

一般情况下我们不考虑压降的影响,但是对于长距离的电源走线,需再增加50%的裕量,增加铜皮的宽度减小这部分的直流电阻。或者在一些对电压有严格要求的地方必须要考虑压降的影响,对于更严格的设计需求,可以用Cadence PDN中的IRDROP(压降)进行仿真。IRDROP很多仿真软件都可以做,例如hyperlynx ,sigrity等,仿真精度都比较高。如图为hyperlynx 做的一个IrDrop仿真图。

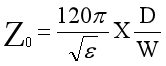

(2)要考虑电源层和地层的阻抗。动态阻抗可以通过仿真工具得到。但对于电源的静态阻抗,可以用下面公式来预估:

其中,D为电源平面同地平面之间的间距。W为平面之间的面积。从上面静态的计算公式,可得出减少直流压降的措施:

(1)电源平面要尽量与地平面靠近,以求减少电源静态内阻。

(2)在满足工艺设计的要求下,电源线和地线要尽量加宽。

(3)尽量把电源放置到地平面以下。

4 参考平面

如果将PCB的信号作为一个回路模型来看,那么地平面层也可以看做传输通道的一部分。因为只有构成完整的回路,整个电路才能正常工作。低频信号的回路会选择电阻最小的路径,而高频数字电路则会选择感抗最小的路径进行回流。这时候,电源地平面就成了信号所选择的低感抗回流通道,也就赋予了参考平面的作用。

当电源、地平面作为参考平面进行设计时,有以下要求需要注意:

(1)避免信号跨越电源地分割,保证信号的参考平面相对完整,这是考虑层叠和EMC设计的首要原则。

(2)层叠对称原则。

(3)元件面下尽量设置一个完整地平面。

5 其他要求

(1)电源、地分割方式简洁合理,分割区域的大小满足载流能力。分割线宽度一方面要满足现在的工艺要求,另一方面要考虑不同电压的压差影响,压差越大,分割线应该越粗。(对于FR4的板子,一般1mm间距可以耐压1000V,当前设计中分割线宽窄实际取决于PCB制造工艺。)在BGA区域需要用相对较细的分割线,以免出现因分割线太粗,导致部分电源引脚没有被有效覆盖而要用另外的层连接。如图11-8所示,BGA区域和BGA外的区域的分割线粗细比较合适。

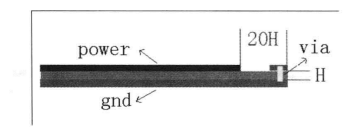

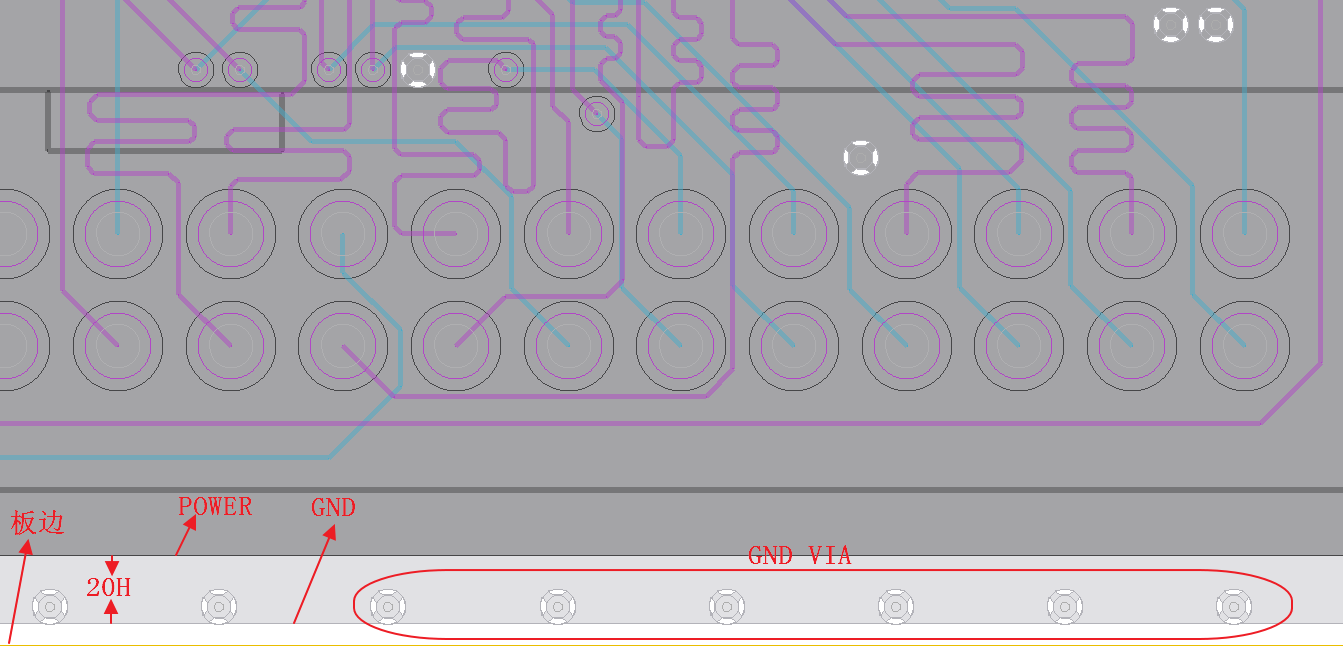

(2)20H准则:在地层的边缘,包括不同性质的地层,地层要比电源层、信号层外延20H,在这里H表示相邻的电源层和地层之间的距离,如图所示。

(3)关键信号不要布在地层的边缘,如果在与电源层相邻的信号层边缘设置一圈地(相当于一个护栏),并将这圈地与地层用间隔(推荐200mil)较密的过孔连接起来,如图所示,会更好地降低辐射。

(3)相邻分割区的电源压差不能过大。如果过大时,需增大隔离线的宽度。

(4)对于高压的处理需满足安全要求。