当一块PCB板完成了布局布线,又检查连通性和间距都没有报错的情况下,一块PCB是不是就完成了呢?答案当然是否定。很多初学者也包括一些有经验的工程师,由于时间紧或者不耐烦亦或者过于自信,往往草草了事,忽略了后期检查。结果出现了一些很基本的BUG,比如线宽不够,元件标号丝印压在过孔上,插座靠得太近,信号出现环路等等。从而导致电气问题或者工艺问题,严重的要重新打板,造成浪费。所以,当一块PCB完成了布局布线之后,很重要的一个步骤就是后期检查。

PCB的检查有很多个细节的要素,本人列举了一些自认为最基本的并且最容易出错的要素,作为后期检查。

1、元件封装

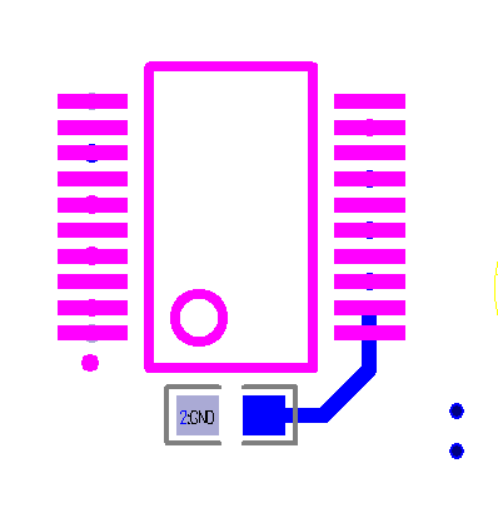

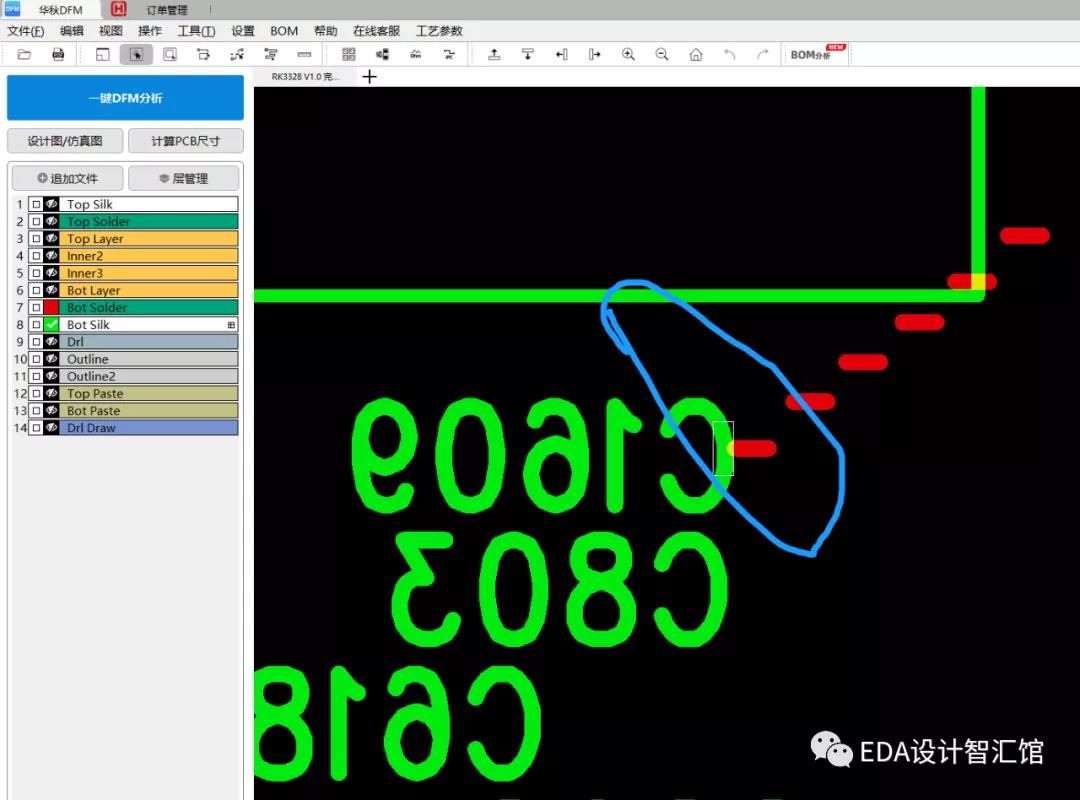

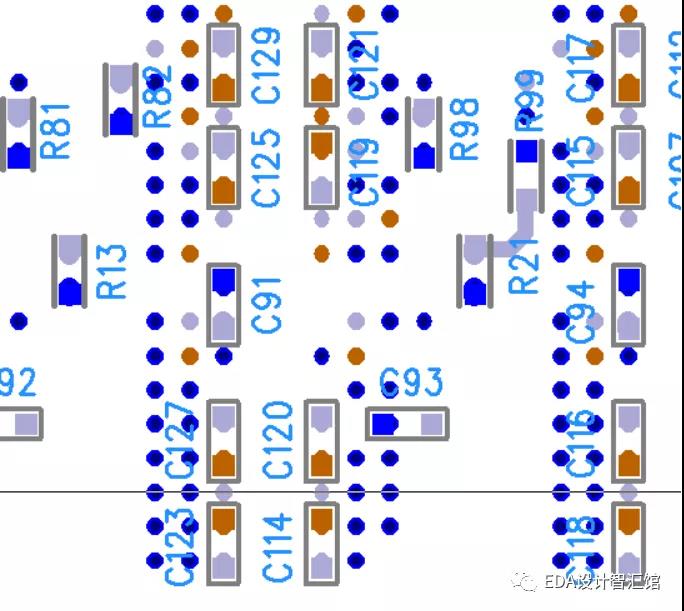

(1)焊盘间距。如果是新的器件,要自己画元件封装,保证间距合适,焊盘间距直接影响到元件的焊接。检查要点:丝印是否上阻焊。

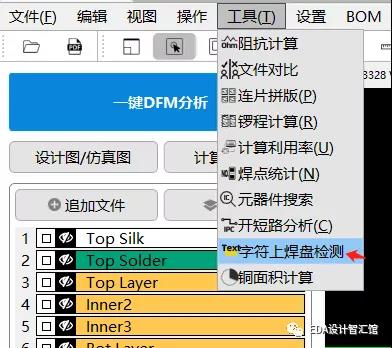

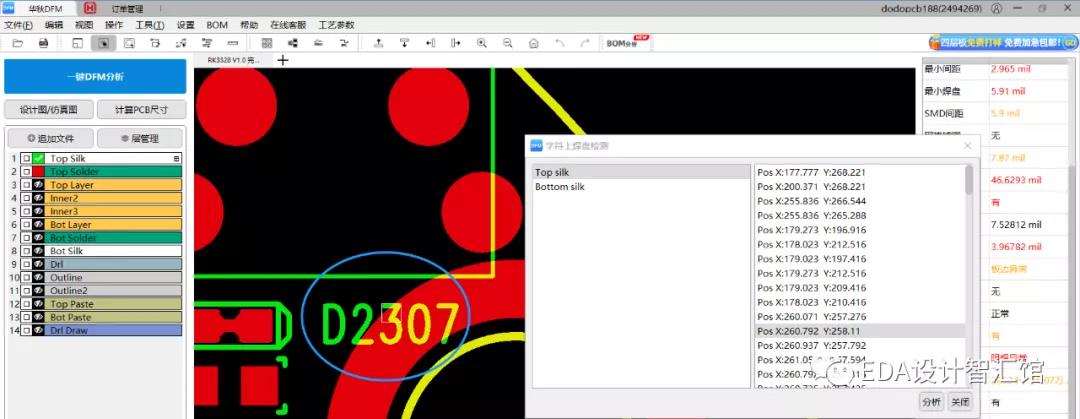

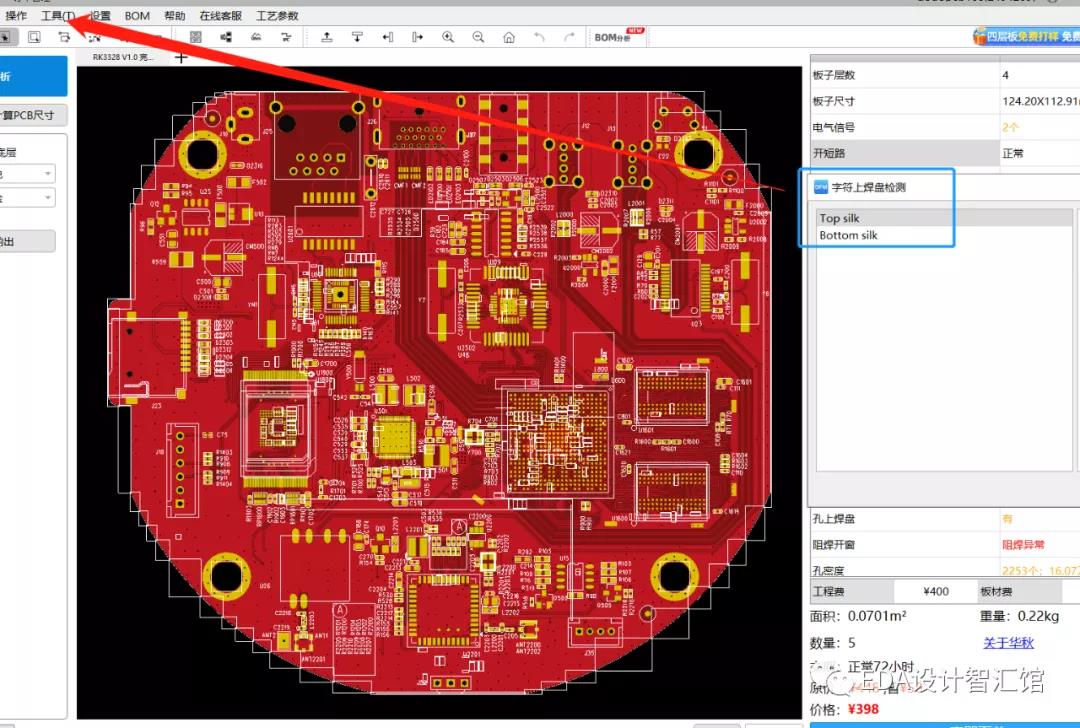

执行:工具->字符上阻焊检查

检测后会列出不符合要求的清单:单击相应的坐标软件会自动跳转到错误的位置,方便设计师修改。

(2)过孔大小。一般保留不小于0.2mm比较合适。

(3)器件的轮廓丝印。器件的轮廓丝印最好比实际大小要大一点。

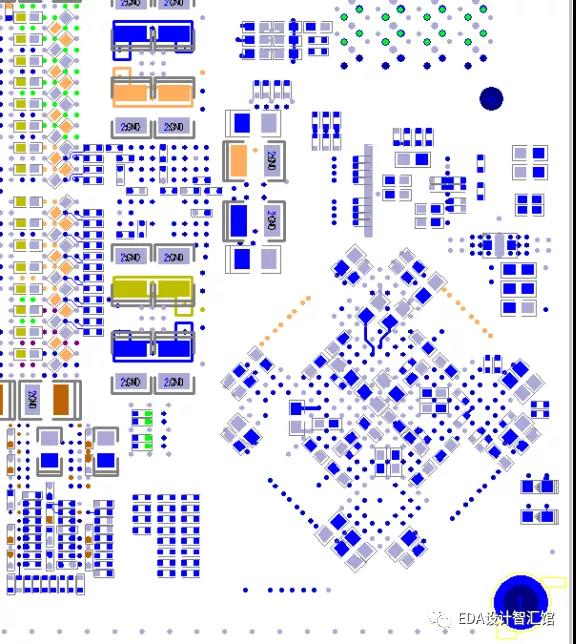

2、布局

| 布局 | 数字和模拟电路是否分开 |

| 高速和低速电路是否分开 | |

| 高压和低压电路是否分开并满足爬电距离 | |

| 相同模块是否布局一致 | |

|

电源模块是否满足以下要求: A.输出电源载流量是否满足(铜皮宽度和过孔数) B.地回路在元件大面积连接 C.电源使能反馈是否独立并取对位置,不在电感下 |

|

| 晶体、晶振及时钟驱动芯片等是否靠近相关器件 | |

|

模拟、射频电路是否一字型或L型布局,主通道线最短 走线加粗,包地,远离电源和高速数字信号 |

|

| 发热量大的器件是否拉开间距 | |

| 保护器件是否靠近接口放置 | |

| DDR拓扑结构是否与客户确认 |

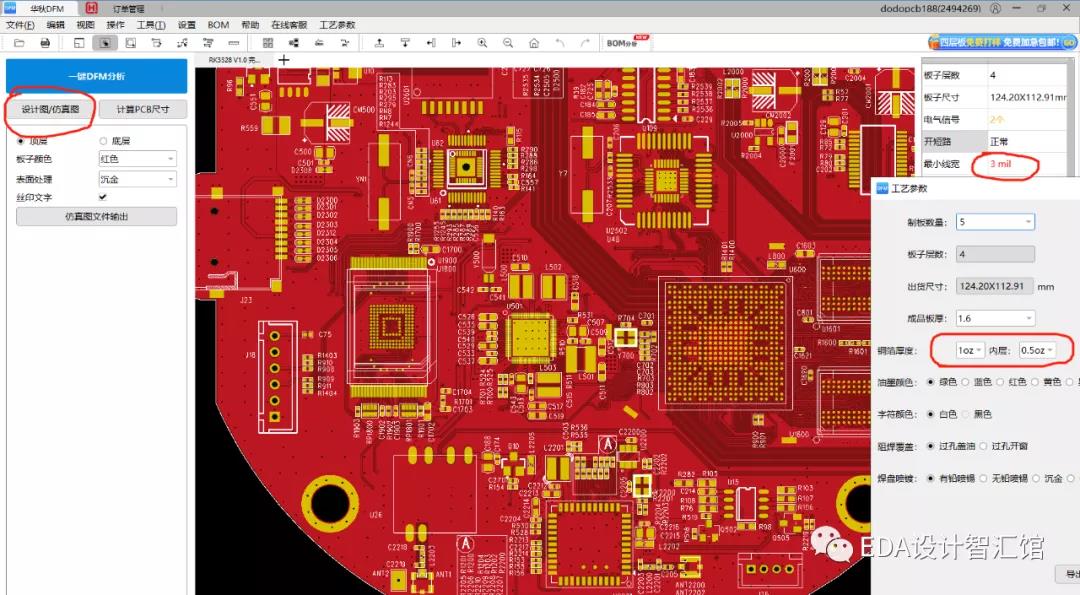

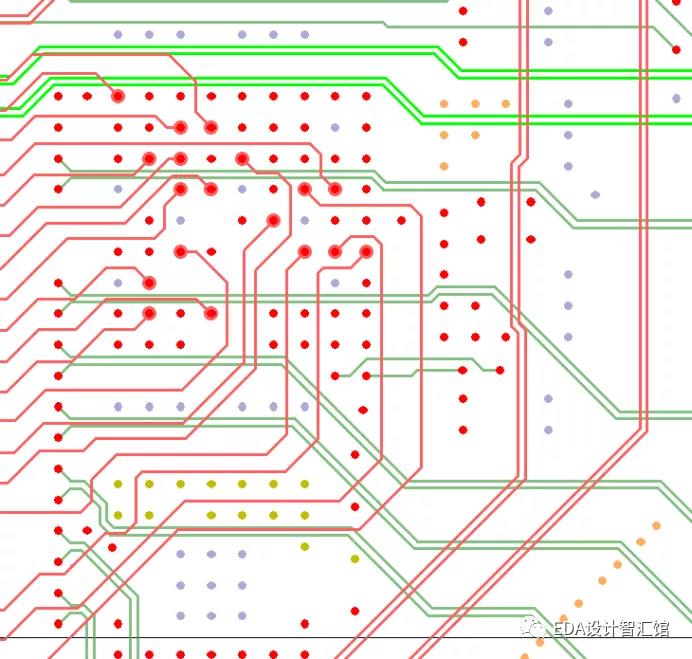

执行:文件导入华秋DFM软件后,在 “设计图/仿真图”进行布局的预览

3、布线

| 布线 |

电感、磁珠等器件两端网络是否已按电源规则处理 (加粗走线或铺铜) |

| 电源层是否比地层内缩20-60mil,并加缝合地孔 | |

|

大电流电源平面是否无瓶颈 满足载流和散热需要 |

|

| SDA/SCL是否走一起 | |

| CLK,RST是否跟其他线拉开间距,能包地包地 | |

| 是否无dangling线,孔,铜皮,是否无线宽突变 | |

| PGND走线是否加粗至2mm,距离其他网络2mm | |

| pin之间边缘间距小于20mil的是否禁止穿线,或尽量不穿 | |

| 变压器,继电器,光耦是否挖空所有层 | |

| 信号是否无跨平面,跨平面单端走线客户是否接受 | |

| 高速差分是否在最佳走线层,STUB是否能够接受 | |

| 高速差分过孔数是否不超过3个, 回流地过孔反焊盘是否增加 | |

| 高速线是否距离板边1mm以上 | |

|

高速差分是否避免穿过 晶振,电感,变压器,继电器,光耦等 |

|

|

相邻层布线方向是否尽可能相互垂直 平行走线时尽量上下 错开布线并避免并行走线过长 |

|

| 建类是否正确 | |

| 差分与差分是否拉开间距 | |

| 等长是否满足要求(如差分对间25mil,对内5mil单端线50mil) |

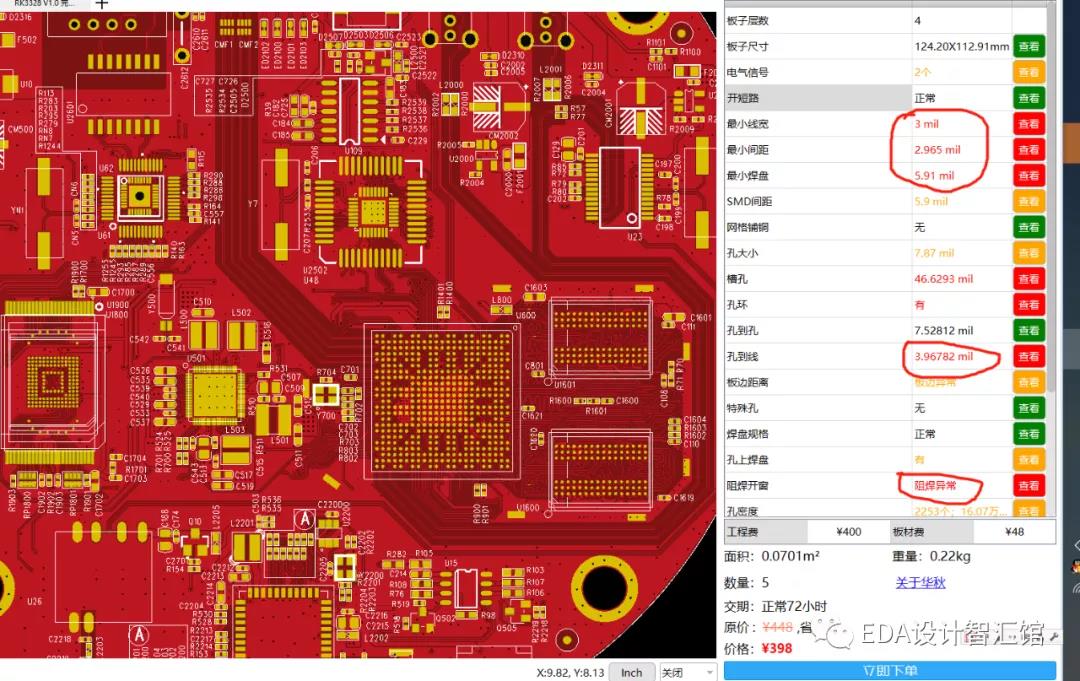

布线检查可通过软件执行:一键智能分析

4、EMC和信号完整性

71、 一对50 欧姆微带传输线中,线间距与线宽相等时,信号线间的耦合电容约占5%。

72、 一对50 欧姆微带传输线中,线间距与线宽相等时,信号线间的耦合电感约占15%。

73、 对于1NS 的上升时间,FR4 中近端噪声的饱和长度是6IN,它与上升时间成比例。

74、 一跟线的负载电容是一个常数,与附近其他线条的接近程度无关。

75、 对于50 欧姆微带线,线间距与线宽相等时,近端串扰约为5%。

76、 对于50 欧姆微带线,线间距是线宽的2 倍时,近端串扰约为2%。

77、 对于50 欧姆微带线,线间距是线宽的3 倍时,近端串扰约为1%。

78、 对于50 欧姆带状线,线间距与线宽相等时,近端串扰约为6%。

79、 对于50 欧姆带状线,线间距是线宽的2 倍时,近端串扰约为2%。

80、 对于50 欧姆带状线,线间距是线宽的3 倍时,近端串扰约为0.5%。

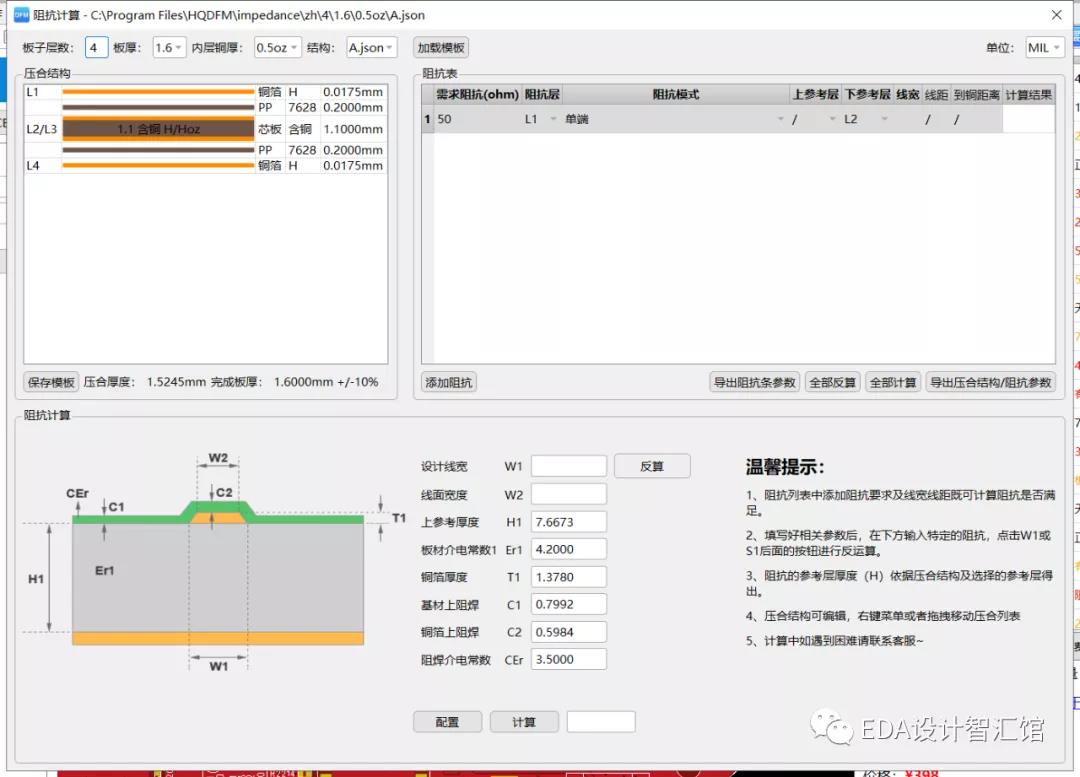

81、特性阻抗。高速信号线需要控制特性阻抗,减少信号反射。高速PCB设计中常用的阻抗设计为单端线50欧,差分线100欧,USB差分线90欧。

执行:工具->阻抗计算,打开阻抗计算模版,输入想要的线宽和阻抗目标值,以及一些基本板材参数,就可以快速得到我们想要的线宽值。

5、丝印

(1)板名、时间、PN码。

(2)标注。对一些接口(如排阵)的管脚或者关键信号进行标注。

(3)元件标号。元件标号要摆放至合适的位置,密集的元件标号可以分组摆放。注意不要摆放在过孔的位置。

执行:工具->字符上阻焊检查

6、其他

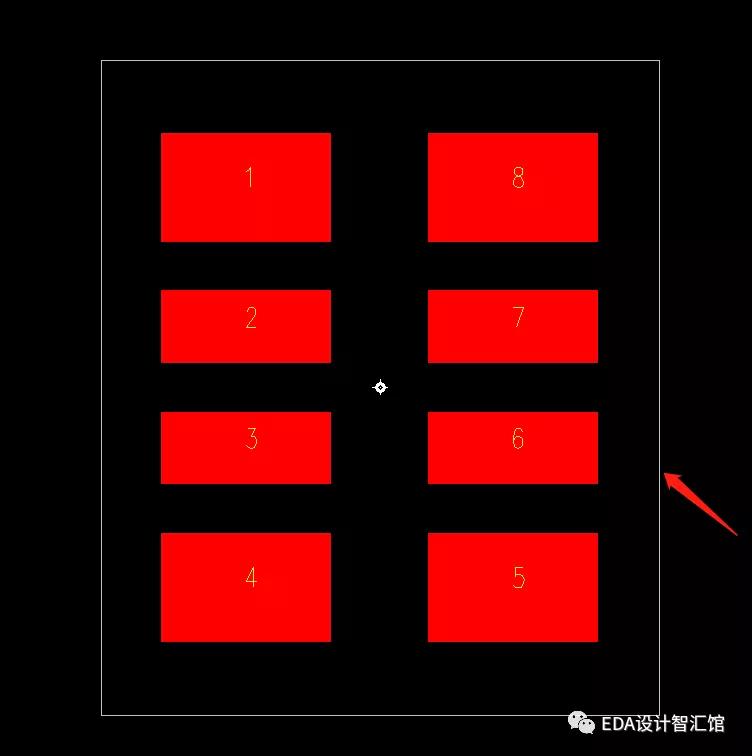

(1)Mark点。

对于需要机器焊接的PCB,需要加入两到三个的Mark点。

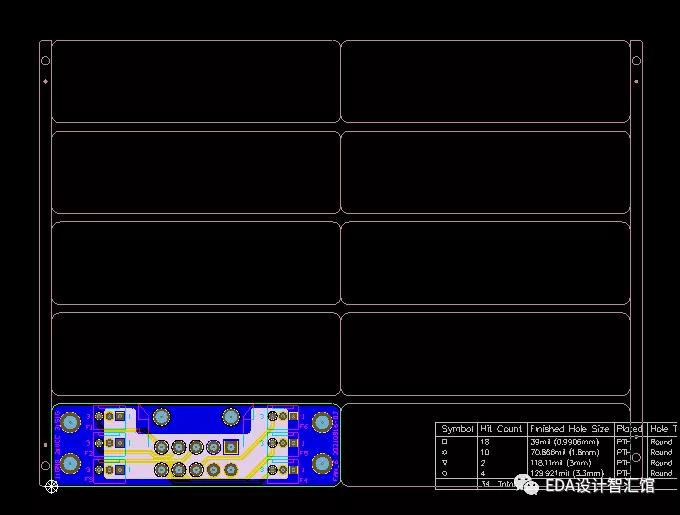

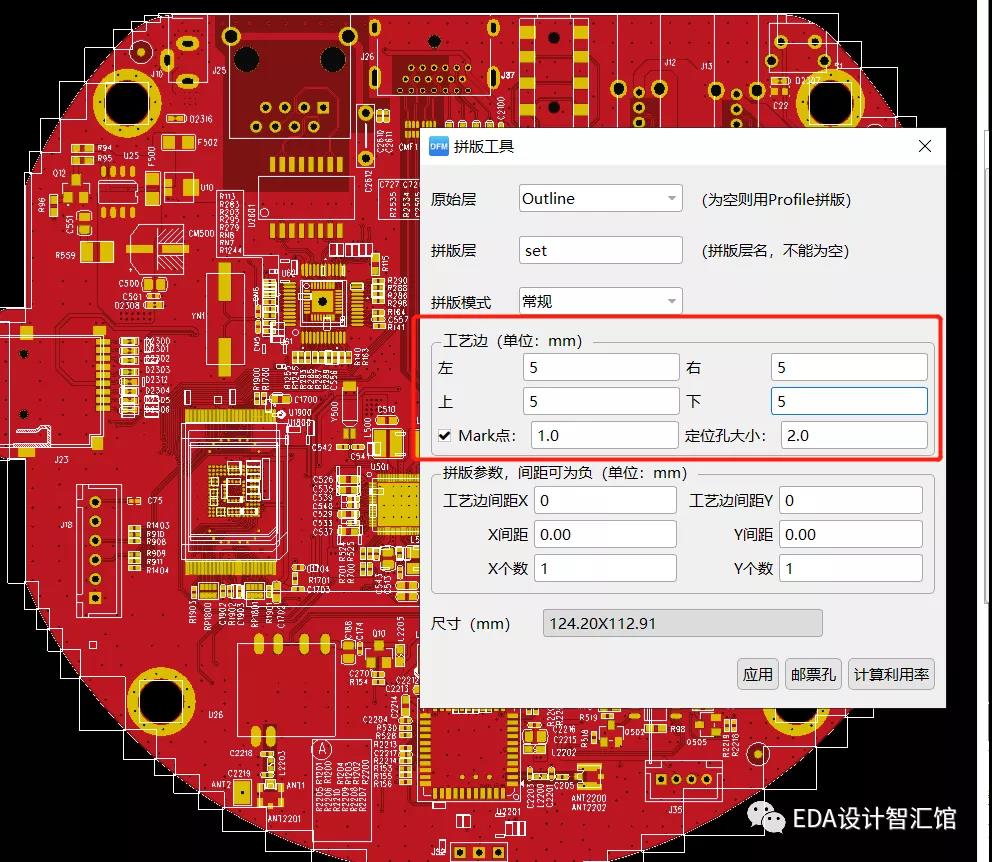

(2)工艺边和拼板。

对于不规则形状的PCB需要进行拼板,并且需要加上工艺边

执行:工具->连片拼板